# TECHNICAL MANUAL

# EXTENDED PERFORMANCE RAPID ACCESS DATA FILE

MODELS 7231/7232

October 1969 (Revised June 1970)

# LIST OF EFFECTIVE PAGES

Total number of pages is 356, as follows:

| Page No.       | Issue             | Page No. | Issue |

|----------------|-------------------|----------|-------|

| Title          | Original          |          |       |

| A              |                   |          |       |

| Foreword       | Original          |          |       |

| i thru x       |                   |          | •     |

| 1-1 thru 1-6   |                   |          |       |

| 2-1 thru 2-4   |                   |          |       |

| 3–1 thru 3–14  | Original          |          |       |

| 4-1 thru 4-152 |                   |          | • .   |

| 5-1 thru 5-24  | S .               |          | •     |

| 6-1 thru 6-30  | G                 | e - Form |       |

| 7-1 thru 7-14  |                   |          | •     |

| 8-1 thru 8-26  |                   |          |       |

| _              | Revised June 1970 | •        | ,     |

| 8-29 thru 8-32 |                   |          | ×.    |

| 9-1 thru 9-66  |                   |          |       |

|                | •                 | •        |       |

# **FOREWORD**

This publication supersedes XDS publication No. 901565A and incorporates the information previously supplied by PDQ No. 70-018.

#### TABLE OF CONTENTS

| Section | Title                                    | Page |

|---------|------------------------------------------|------|

| I       | INTRODUCTION                             | 1-1  |

| , -     | 1-1 Scope of Manual                      | 1-1  |

|         | 1-2 Organization of Manual               | 1-1  |

|         | 1-3 Description                          | 1-1  |

|         | 1-4 EP RAD File                          | 1-1  |

|         | 1–5 EP RAD Controller                    | i-1  |

|         | 1-6 EP RAD Selection Unit                | 1-5  |

|         | 1-7 Disc File                            | 1-5  |

|         | 1-8 Motor Control Assembly               | 1-5  |

|         | 1-9 Power Distribution Panel             | 1-5  |

|         | 1–10 Power Supply Model PT20             | 1-5  |

| II.     | OPERATION AND PROGRAMMING                | 2-1  |

|         | 2-1 General                              | 2-1  |

|         | 2-2 Controls                             | 2-1  |

|         | 2-3 EP RAD Controller Address Switches   | 2-1  |

|         | 2-4 EP RAD Storage Unit Address Switches | 2-1  |

|         | 2-5 Online/Offline Switch                | 2-1  |

|         | 2-6 Memory Protection Switches           | 2-1  |

|         | 2-7 Power Distribution Panel             | 2-3  |

|         | 2-8 Motor Control Assembly               | 2-3  |

|         | 2-9 Powar Supply Model PT20              | 2-3  |

|         | 2-10 Operating Procedures                | 2-3  |

|         | 2-11 Programming.                        | 2-3  |

|         | 2–12 Instructions                        | 2-3  |

|         | 2–13 Sample Program                      | 2-3  |

| lil     | FUNCTIONAL OPERATION                     | 3-1  |

|         | 3-1 General                              | 3-1  |

|         | 3-2 Data Organization                    | 3-1  |

|         | 3–3 Mechanical Functions                 | 3-1  |

|         | 3-4 Power Distribution                   | 3-4  |

|         | 3-4 Power Distribution                   | 3-4  |

|         | 3-6 IOF Interface                        | 3-4  |

|         | 3-7 AIO Command                          | 3-4  |

|         | 3-8 HIO Command                          | 3-4  |

|         | 3-9 TDV Command                          | 3-4  |

|         | 3-10 TIO Command                         | 3-6  |

|         | 3–11 SIO Command                         | 3-6  |

|         | 3-12 Internal Operations                 | 3-6  |

|         | 3-13 Seek Order                          | 3-6  |

|         | 3-14 Sense Order                         | 3-7  |

|         | 3-15 Write Order                         | 3-7  |

|         | 3-16 Read Order                          | 3-1  |

|         | 3-17 Checkwrite Order                    | 3-13 |

|         | 3-18 Selection Unit Interface            | 3-13 |

|         | 3-19 EP RAD Selection Unit               | 3-13 |

# XDS 901565

# TABLE OF CONTENTS (Conf.)

| ection |        | Title                                               | Page |

|--------|--------|-----------------------------------------------------|------|

| IV     | PRINCI | IPLES OF OPERATION                                  | 4-1  |

|        | 4-1    | Scope and Organization of Section                   | 4-1  |

|        | 4-2    | Electromechanical Operation                         | 4-1  |

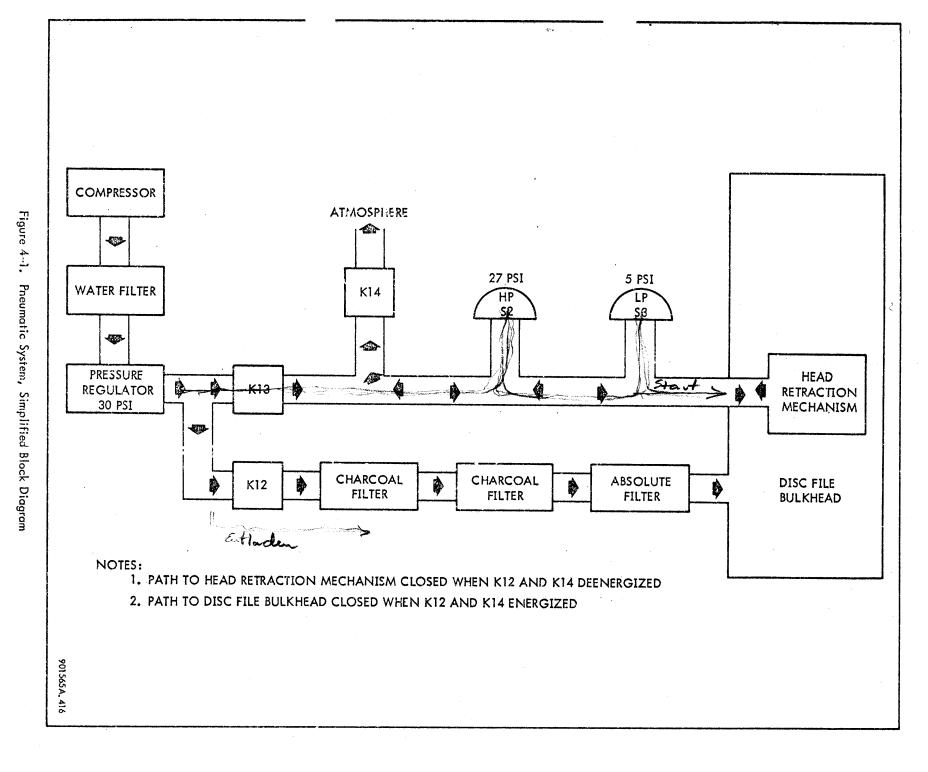

|        | 4-3    | Pneumatic System                                    | 4-1  |

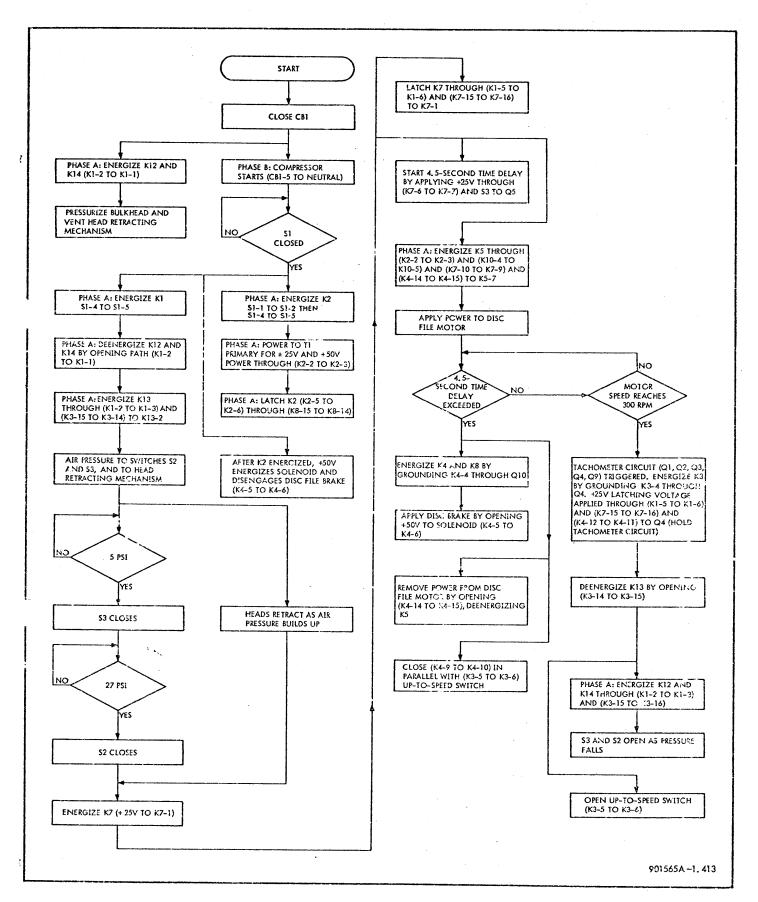

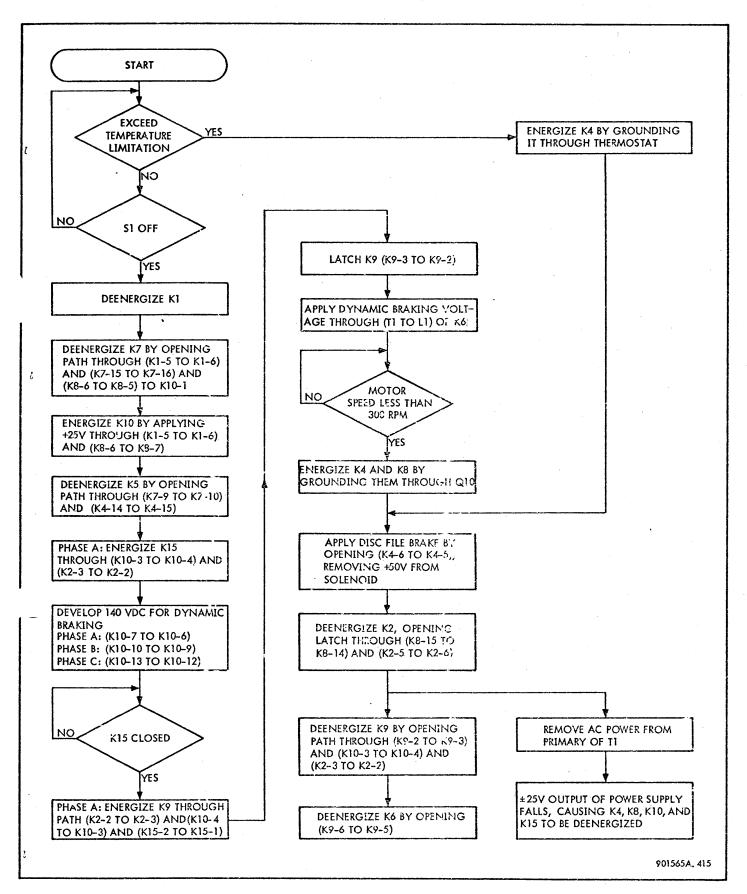

|        | 4-4    | Motor Control Assembly                              | 4-1  |

|        | 4-5    | Power Distribution                                  | 4-3  |

|        | 4-6    | Power Distribution Panel                            | 4-3  |

|        | 4-7    | Power Fail-Safe Circuits                            | 4-3  |

|        | 4-8    | EP RAD Controller                                   | 4-3  |

|        | 4-9    | Subcontroller                                       | 4-3  |

|        | 4-10   | Function Strobe and Function Indicators             | 4-8  |

|        | 4-11   | IOP Data Line Signals                               | 4-8  |

|        | 4-12   | Priority Signals                                    | 4-8  |

|        | 4-13   | Subcontroller Response                              | 4-9  |

|        | 4-14   | TDV Function Indicator                              | 4-9  |

|        | 4-15   | TIO Function Indicator                              | 4-9  |

|        | 4-16   | HIO Function Indicator.                             | 4-10 |

|        | 4-17   | SIO Function Indicator                              | 4-10 |

|        | 4-17   | AIO Function Indicator                              | 4-11 |

|        | 4-19   | ASC Function Indicator                              | 4-11 |

|        |        | Phase Control Circuits                              | 4-12 |

|        | 4-20   | ***************************************             | 4-13 |

|        | 4-21   | TCL Delay Line                                      | 4-13 |

|        | 4-22   | Phase Flip-Flops                                    | 4-13 |

|        | 4-23   | Response to IOP Commands                            | 4-13 |

|        | 4-24   | Order Out Sequence                                  | 4-22 |

|        | 4-25   | Seek Order Sequence                                 |      |

|        | 4-26   | Sense Order Sequence                                | 4-24 |

|        | 4-27   | Write Order or Checkwrite Order Sequence            | 4-25 |

|        | 4-28   | Read Order Sequence                                 | 4-26 |

|        | 4-29   | Order In Sequence                                   | 4-27 |

|        | 4-30   | Service Cycle Identification Logic                  | 4-28 |

|        | 4-31   | Order Register                                      | 4-29 |

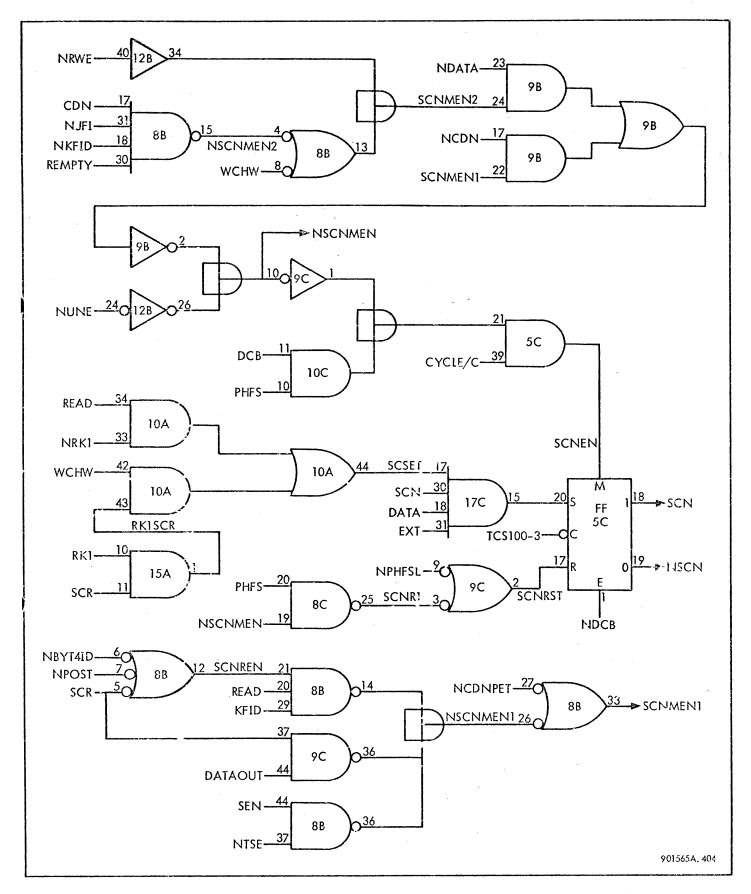

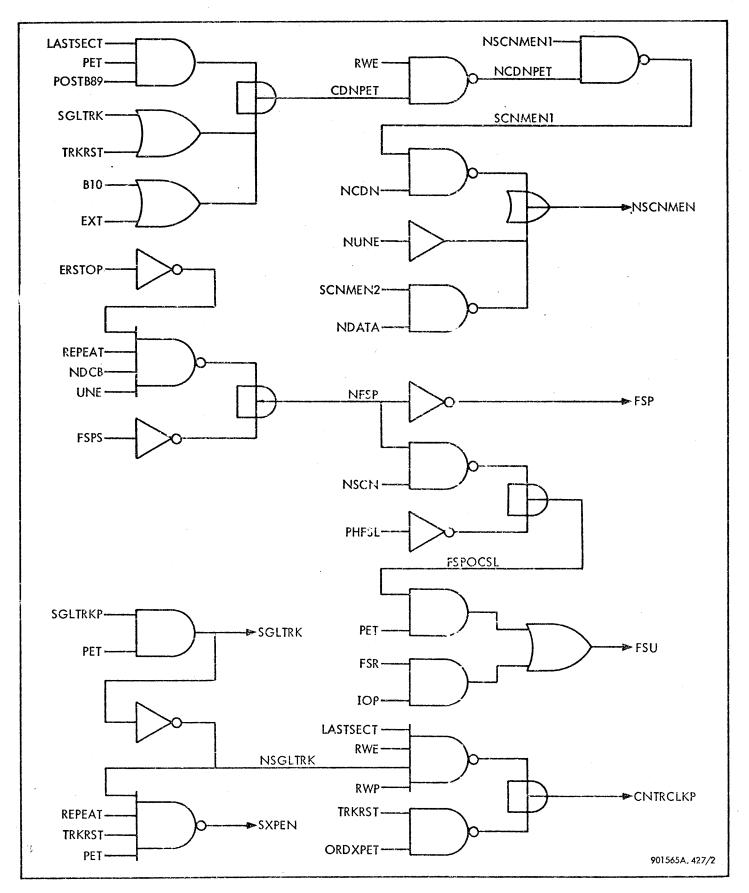

|        | 4-32   | Service Call Logic                                  | 4-30 |

|        | 4-33   | Byte Counter                                        | 4-32 |

|        | 4-34   | Terminal Order Operations                           | 4-33 |

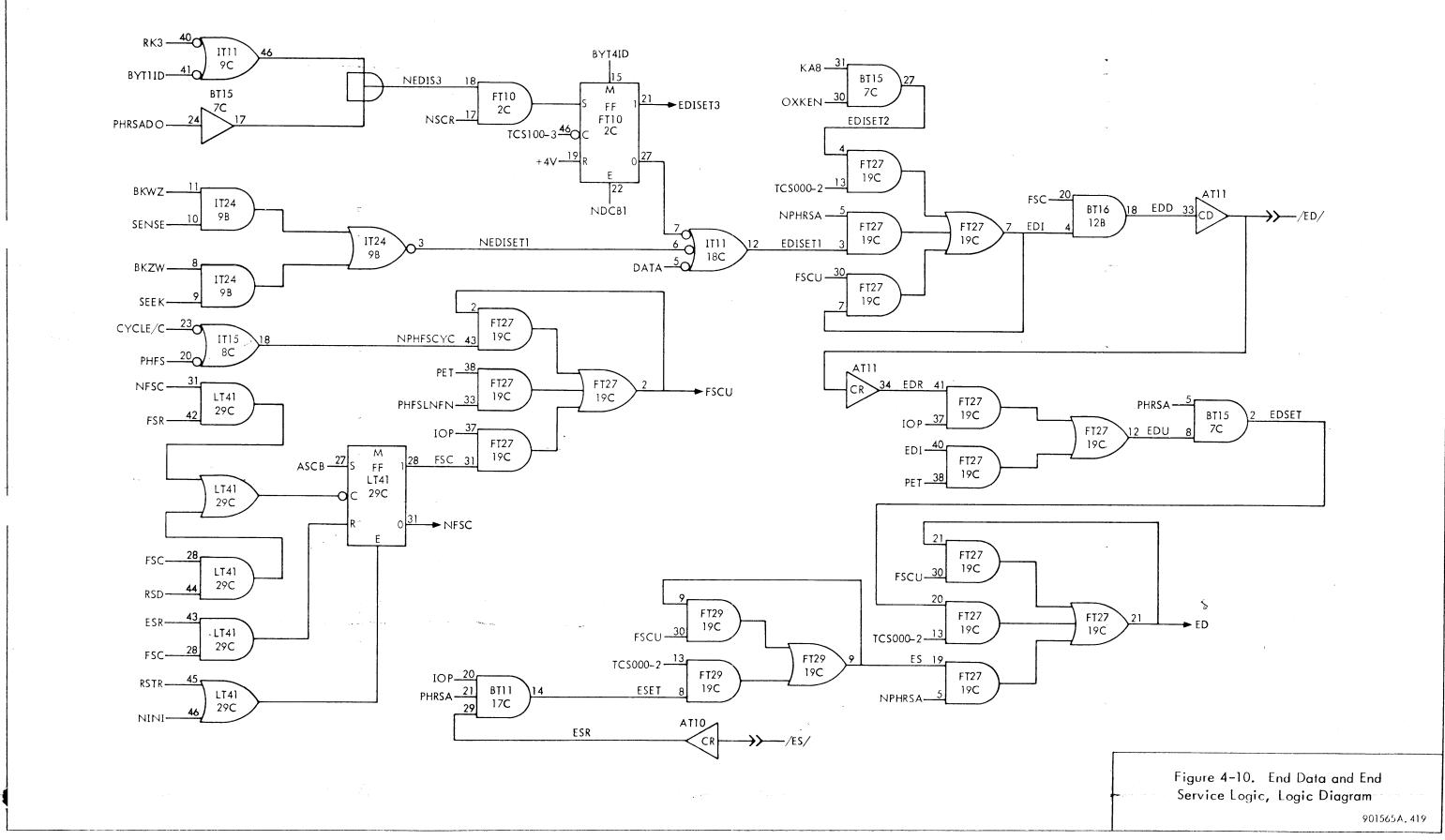

|        | 4-35   | Ena Data and End Service Logic                      | 4-34 |

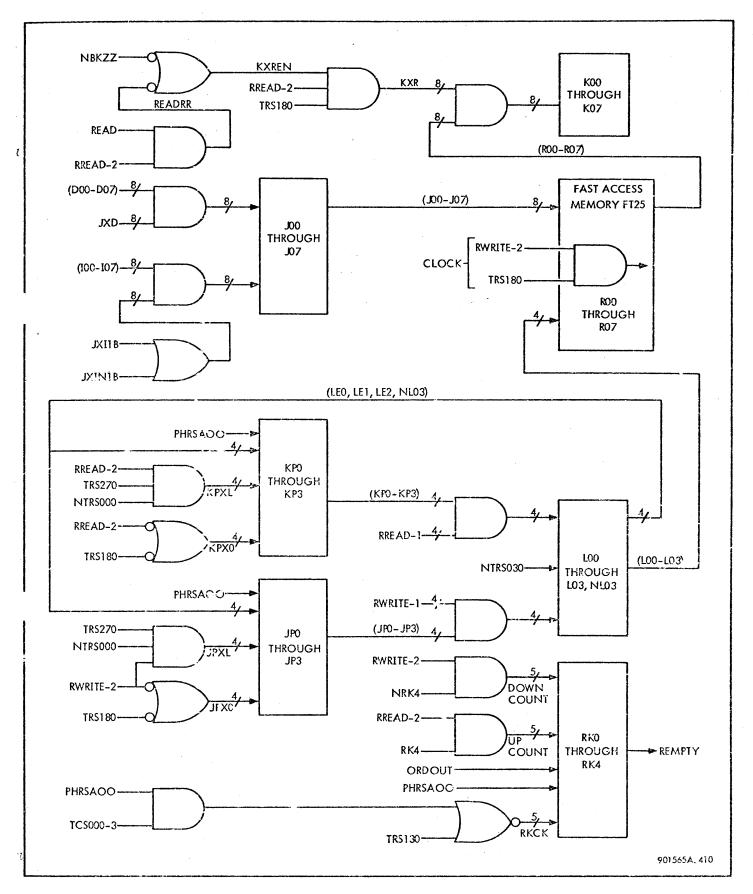

|        | 4-36   | Input/Output Data Buffer                            | 4-37 |

|        | 4-37   | I-Register                                          | 4-37 |

|        | 4-38   | O-Register                                          | 4-39 |

|        | 4-39   | J-Register                                          | 4-40 |

|        | 4-40   | Fast Access Memory (FAM) Circuits                   | 4-41 |

|        | 4-41   | TRL Delay Line                                      | 4-41 |

|        | 4-42   | RK-Counter                                          | 4-45 |

|        | 4-43   | J. Register                                         | 4-48 |

|        | 4-44   | KF-Register                                         | 4-48 |

|        | 4-45   | L-kegister                                          | 4-51 |

|        | 4-46   | Operation of FAM Circuits During the Write Sequence | 4-52 |

|        | 4-47   | One-Byte Interface                                  | 4-52 |

|        | 4-48   | Multiple-Byte Interface                             | 4-54 |

|        | 4-49   | Operation of FAM Circuits During the Read Sequence  | 4-55 |

|        | 4-50   | One-Byte Interface                                  | 4-55 |

|        | 4-51   | Multiple-Byte Interface                             | 4-56 |

|        | 4-52   | Operation of the TRL Delay Line for a Seek Order    | 4-57 |

# TABLE OF CONTENTS (Cont.)

| Section |                | Title                                            | Page  |

|---------|----------------|--------------------------------------------------|-------|

|         | 4-53           | Selection Unit Interface Circuits                | 4 50  |

|         | 4-54           | TDL Delay Line                                   | 4-58  |

|         | 4-55           | Interface Clocking                               | 4-58  |

|         | 4-56           | B-Counter                                        | 4-60  |

|         | 4-57           | K-Register                                       | 4-60  |

|         | 4-58           | D-Register                                       | 4-63  |

|         | 4-59           | Interface Control Circuits                       | 4-63  |

|         | 4-60           | Track Shift Sequence                             | 4-65  |

|         | 4-61           | Write Order Sequence                             | 4-65  |

|         | 4-62           | Read Order Sequence                              | 4-66  |

|         | 4-63           | Checkwrite Order Sequence                        | 4-68  |

|         | 4-64           | Sense Order Sequence                             | 4-69  |

|         | 4-65           | Addressing Circuits                              | 4-70  |

|         | 4-66           | P-Register                                       | 4-70  |

|         | 4-67           | S-Register                                       | 4-70  |

|         | 4-68           | T-Register                                       | 4-71  |

|         | 4-69           | U-Register                                       | 4-71  |

|         | 4-70           | Address Incrementation                           | 4-72  |

|         | 4-71           | Checksum Generation                              | 4-72  |

|         | 4-72           | Error Circuits                                   | 4-74  |

|         | 4-73           |                                                  | 4-76  |

|         | 4-74           | Unusual End Logic                                | 4-76  |

|         | 4-75           | Parity Error Logic Write Protect Violation Logic | 4-77  |

|         | 4-76           | Chackwrite Error Logic                           | 4-77  |

|         | 4-77           | Checkwrite Error Logic                           | 4-77  |

|         | 4-78           |                                                  | 4-78  |

|         | 4-79           | Rate Error Logic                                 | 4-79  |

|         | 4-80           | Incorrect Length Logic                           | 4-79  |

|         | 4-81           | Interface Type Logic                             | 4-80  |

|         | 4-82           | Byte Width Logic                                 | 4-90  |

|         | 4-83           | RAD Type Logic                                   | 4-80  |

|         | 4-84           | Online/Offline Control                           | 4-80  |

|         | 4 <b>-</b> 85  | Resat Control                                    | 4-81  |

|         | 4-86           | Reset Control                                    | 4-82  |

|         | 4-87           | IOP Simulation                                   | 4-82  |

|         | 4-88           | Single Phase Mode                                | 4-85  |

|         | 4-89           | Alternate Orders Mode                            | 4-86  |

|         | 4-90           |                                                  | 4-86  |

|         | 4-91           | Count Done Simulation                            | 4-89  |

|         | 492            | Single Track Mode                                | 4-89  |

|         | 4-93           | Error Stop Mode                                  | 4-89  |

|         | 4-94           | 1OP Command Sequences                            | 4-90  |

|         | 4-95           | Order Out Sequence                               | 4-90  |

|         | 4-96           | Sense Order Sequence                             | 4-90  |

|         | 4-97           | Seek Order Sequence                              | 4-106 |

|         | 4-98           |                                                  | 4-109 |

|         | 4-99           | Write Order Sequence                             | 4-109 |

|         | 4-100          | Read Order Sequence                              | 4-121 |

|         | 4-101          | Checkwrite Order Sequence                        | 4-121 |

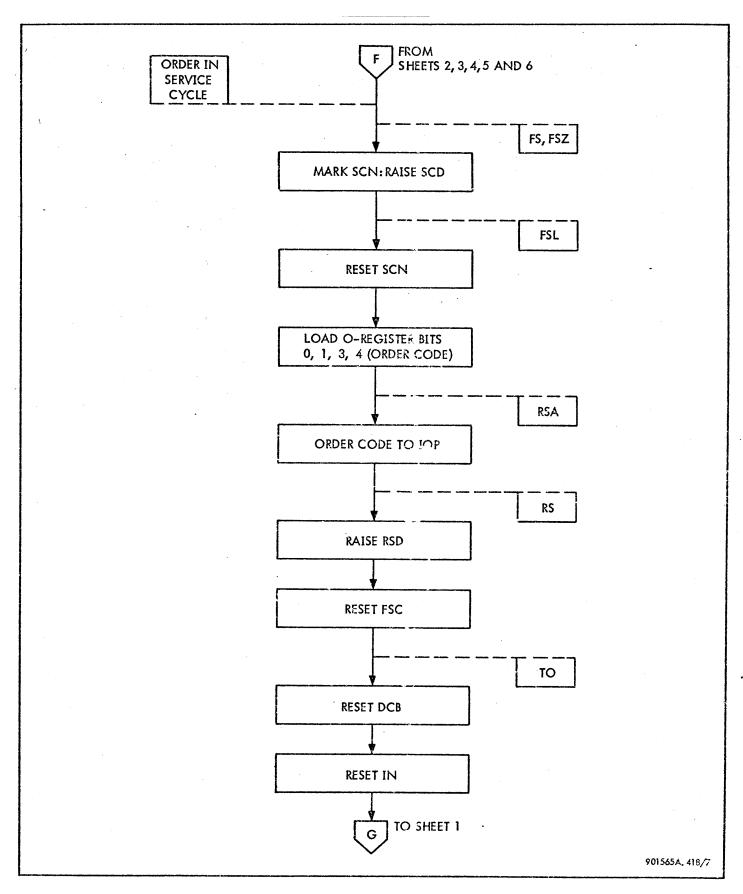

|         | 4-101          | Order In Service Cycle                           | 4-121 |

|         | 4-102          | Terminal Order Operations                        | 4-133 |

|         | 4-103<br>4-104 | EP RAD Selection Unit                            | 4-134 |

|         | 4-104<br>4-105 | Address Circuits                                 | 4-134 |

|         | 4-105          | Track Register                                   | 4-134 |

|         | 4~100          | Memory Protect Circuits                          | 4-134 |

### XDS 901565

# TABLE OF CONTENTS (Cont.)

| Section |            | Title                                            | Page       |

|---------|------------|--------------------------------------------------|------------|

|         | 4-107      | Angle Register                                   | 4-134      |

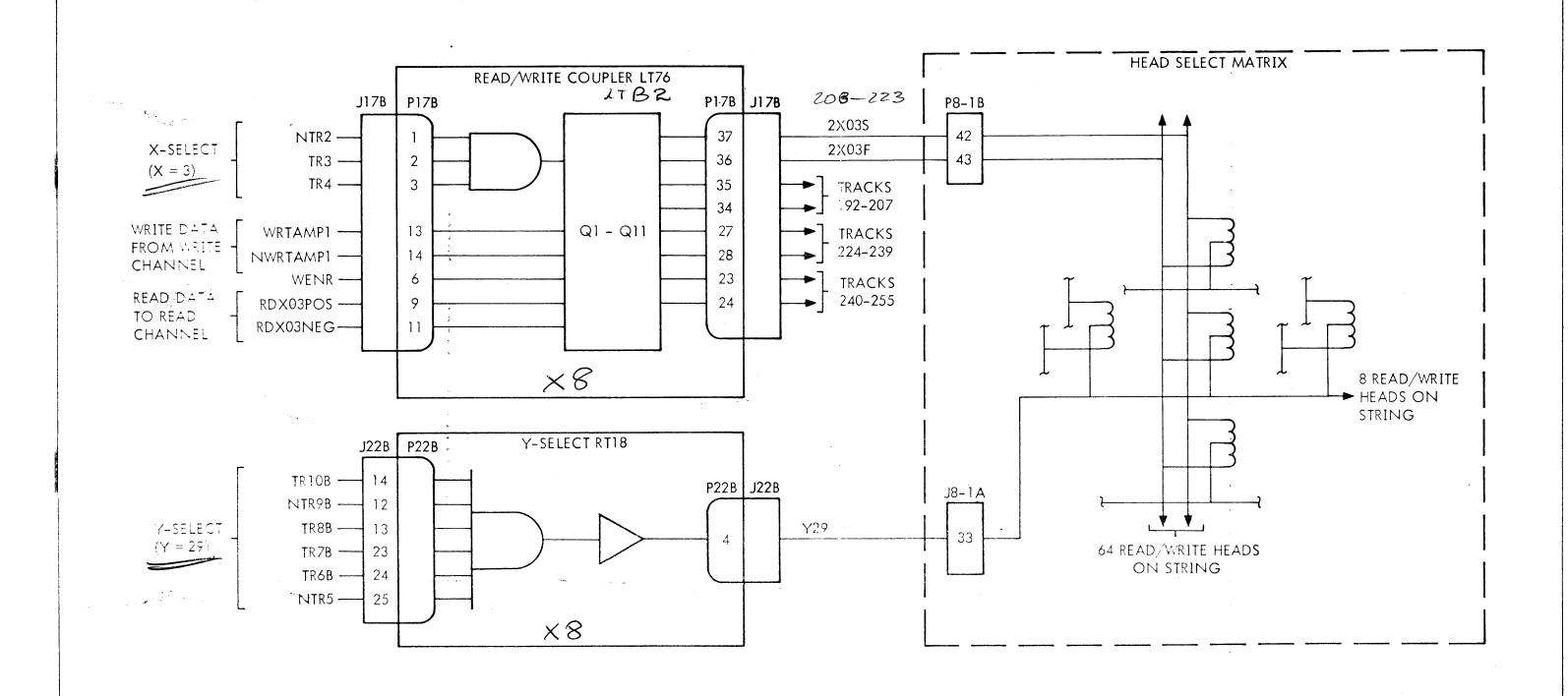

|         | 4-108      | Head Selection Matrix                            | 4-130      |

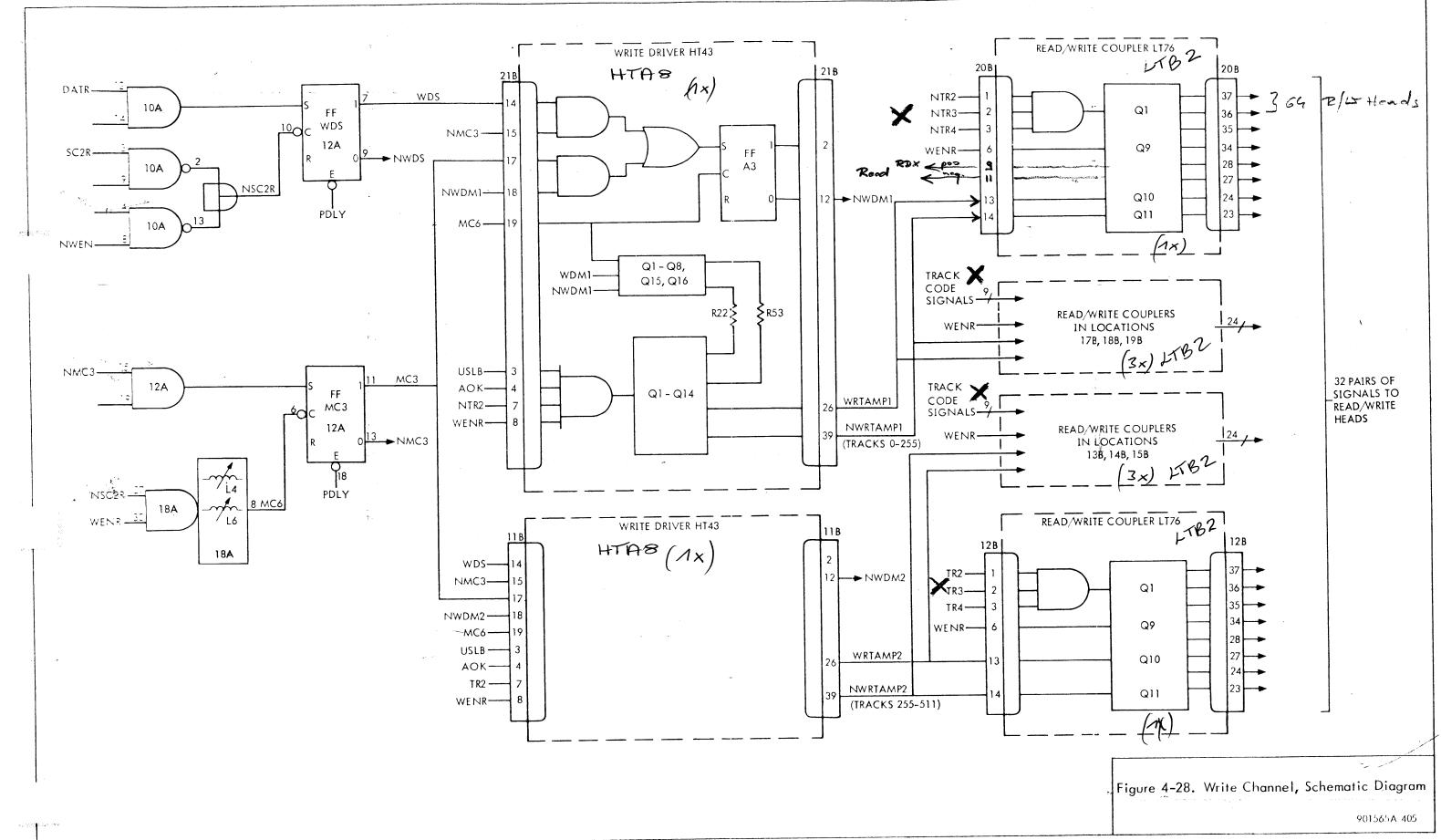

|         | 4-109      | Write Channel                                    | 4-138      |

|         | 4-110      | Read Channel                                     | 4-138      |

|         | 4-111      | Logical Sparing Circuits                         | 4-14       |

|         | 4-112      | Typical Operation                                | 4-14       |

| V       |            | EQUATIONS AND GLOSSARIES                         | 5-1        |

|         | 5-1        | Glossaries                                       | 5-1        |

|         | 5-2        | Logic Equations                                  | 5-1        |

| VI      |            | NGS                                              | 6-1        |

|         | 6-1        | Scope of Section                                 | 6-1        |

|         | 6-2        | Location of Related Text                         | 6-1        |

| VII     | SPECIFI    | CATIONS AND INSTALLATION DATA                    | 7-1        |

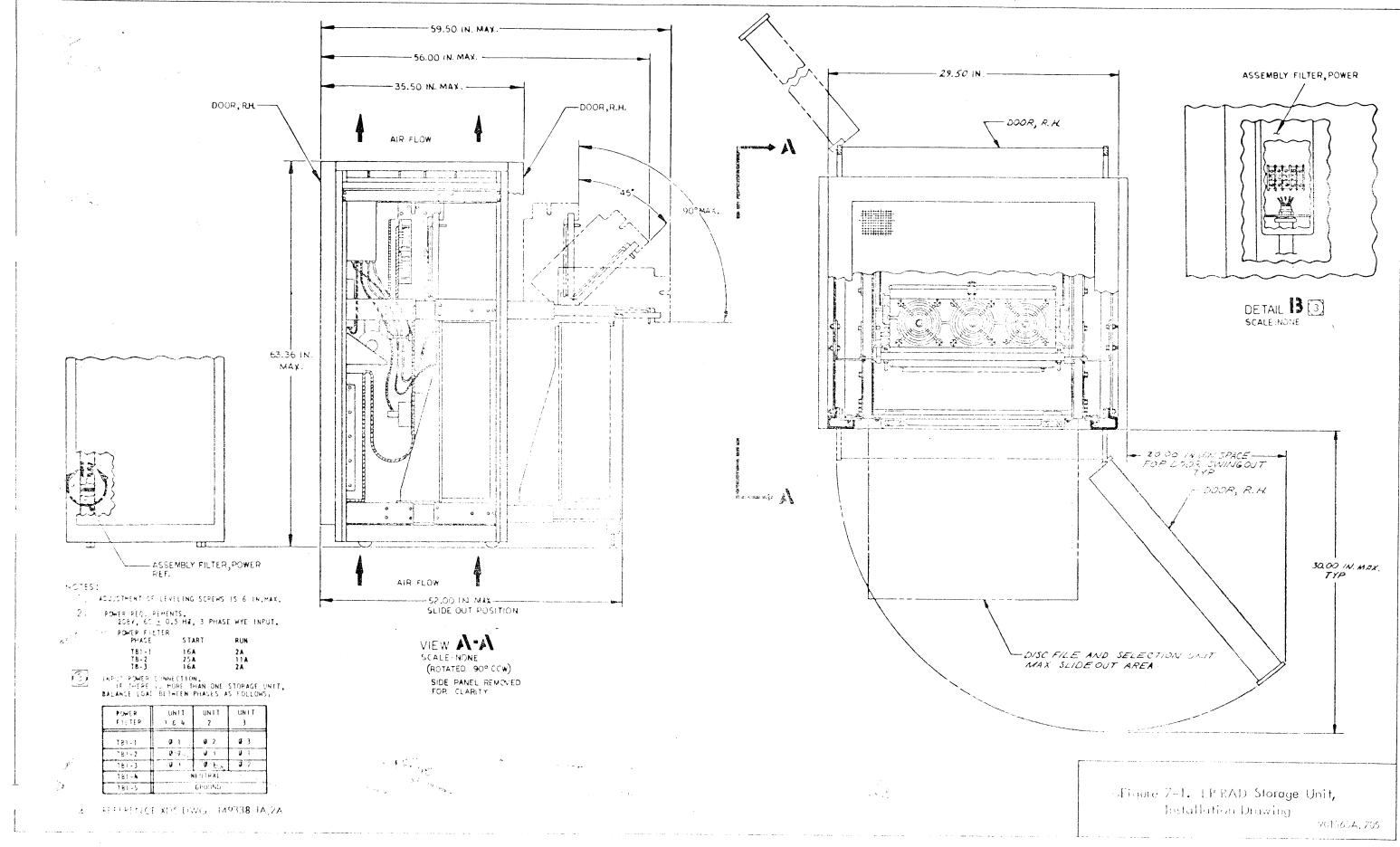

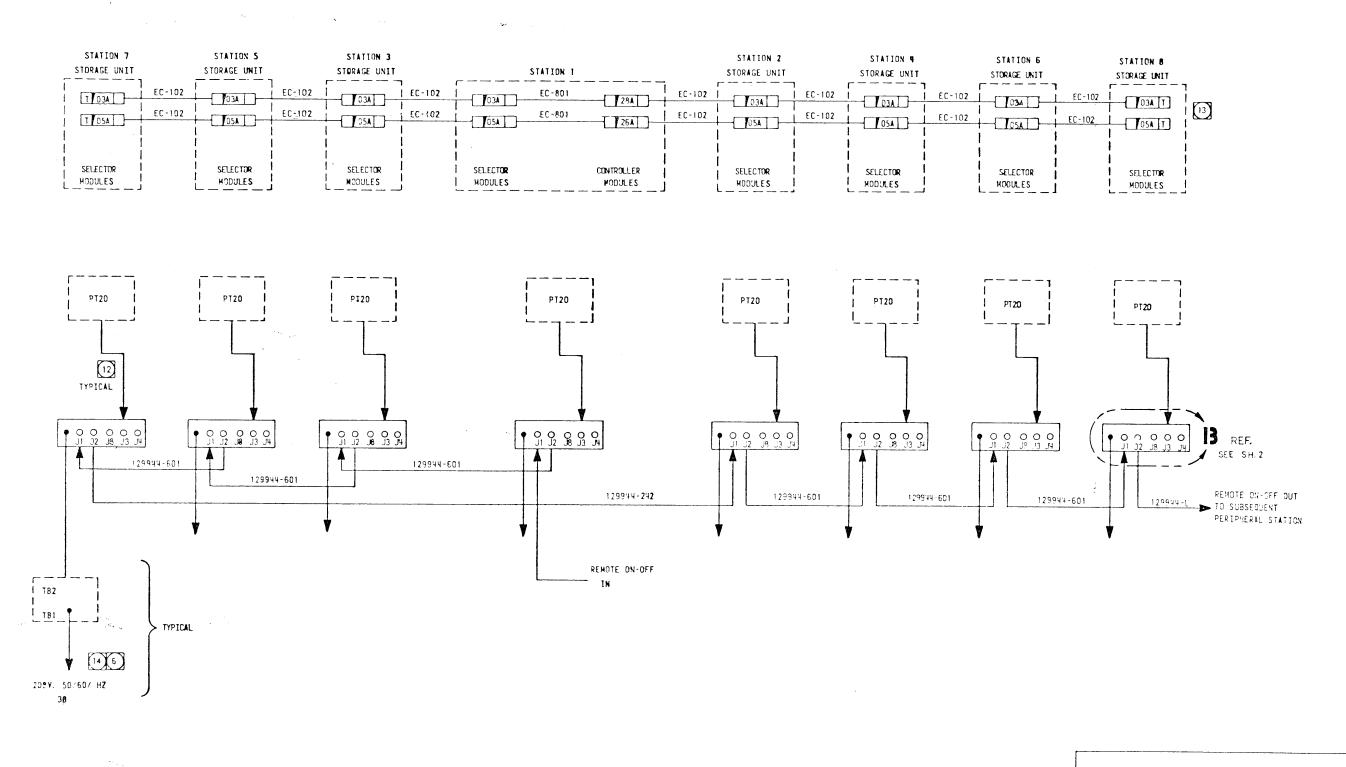

|         | 7-1        | Specifications                                   | 7-1        |

|         | 7-2        | Installation                                     | 7-1        |

|         | 7-3        | Installation Requirements                        | 7-1        |

|         | 7-4        | Installation Procedure                           | 7-1        |

|         | 1111517    | TALLANICE                                        |            |

| VIII    |            | ENANCE                                           | 8-1        |

|         | 8-1<br>8-2 | Scope of Section                                 | 8-1        |

|         | 8-2<br>8-3 | General Maintenance                              | 8-1        |

|         | 8-3<br>8-4 | Diagnostic Test Programs                         | 8-1        |

|         | 8-5        | Preliminary Operations                           | 8-1        |

|         | 8-6        | Power Test                                       | 8-1<br>8-2 |

|         | 8-7        | Adjustment of Timing Signals                     | 8-2        |

|         | 8-8        | Power Fail-Safe Test                             | 8-2        |

|         | 8-9        | Adjustment of AT41 Write Clock Driver            | 3~4        |

|         | 8-10       | Data Path Timing Adjustment                      | S-5        |

|         | 8-11       | Offline Tests                                    | 8-7        |

|         | 8-12       | Preliminary Operations                           | 3-7        |

|         | 8-13       | Single Phase Sequences                           | 8-9        |

|         | 8-14       | Illegal Order Sequence                           | 8-10       |

|         | 8-15       | Single Phase Seek Order                          | 8-10       |

|         | 8-16       | Single Phase Sense Order                         | 8-11       |

|         | 8-17       | Repeat Mode Seek Order                           | 8-12       |

|         | 8-18       | Single Phase Write Order                         | 8-12       |

|         | 8-19       | Sector Counter Test                              | 8-13       |

|         | 8-20       | Extended Interface Test (Two-Byte Option)        | 8-13       |

|         | 8-21       | Extended Interface Test (Four-Byte Option)       | 8-15       |

|         | 8-22       | Repeat Mode Write Order                          | 8-15       |

|         | 8-23       | Y-Select Test                                    | 8-15       |

|         | 8-24       | TCL Delay Line Test                              | 8-16       |

|         | 8-25       | TRL Delay Line Test                              | 8-17       |

|         | 8-26       | Write Amplifier Test                             | 8-17       |

|         | 8-27       | Checkwrite Test                                  | 8-20       |

|         | 8-28       | Alternate Orders Mode, Repeated Operation        | 8-21       |

|         | 8-29       | Alternate Orders Mode, Single Track Operation    | 8-22       |

|         | 8-30       | CPU Mode Tests                                   | 8-22       |

|         | 8-31       | Sigma 5 or Sigma 7 Machine Language Test Program | 8-22       |

|         | 8-32       | Sigma 2 Machine Language Test Program            | 8-22       |

# TABLE OF CONTENTS (Cont.)

| Section |        | Title                                      | Page |

|---------|--------|--------------------------------------------|------|

|         | 8-33   | Repairs, Replacements, and Adjustments     | 8-22 |

|         | 8-34   | Replacement of the Drive Motor Stator      | 8-22 |

|         | 8-35   | Adjustment of the Disc File Brake          | 8-26 |

|         | 8-36   | Replacement of the Disc File Brake Linings | 8-27 |

|         | 8-37   | RAD Filter Replacement                     | 8-27 |

|         | 8-38   | RAD Interface Connector Cleaning Procedure | 8-28 |

|         | 8-39   | Selection of a Spare Write Clock           | 8-28 |

|         | 8-40   | Logical Sparing of Read/Write Head         | 8-30 |

|         | 8-41   | Selection of Spare Read/Write Heads        | 8-30 |

| ΙX      | ILLUST | RATED PARTS BREAKDOWN                      | 9-1  |

|         | 9-1    | Group Assembly Parts List                  | 9-1  |

|         | 9-2    | Numerical Index                            | 9-1  |

### LIST OF ILLUSTRATIONS

| Figure | Title                                                    | Page |

|--------|----------------------------------------------------------|------|

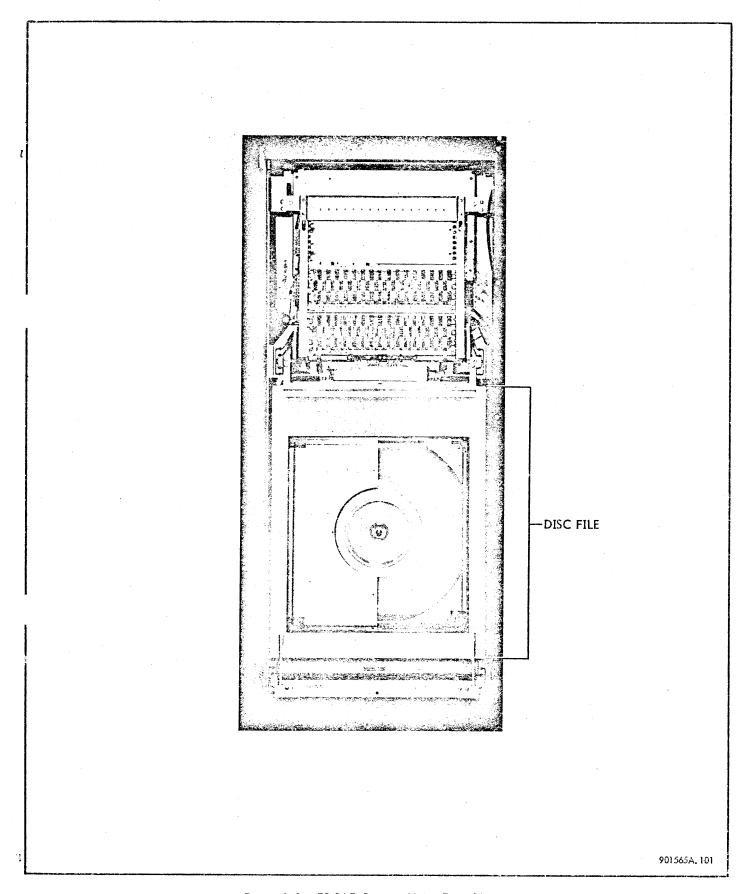

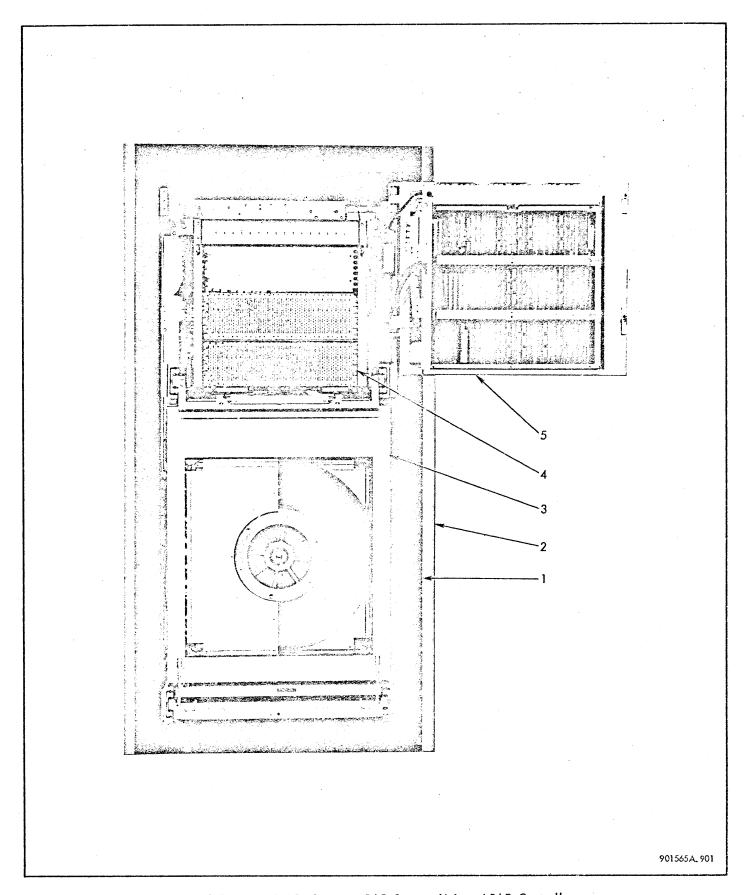

| 1-1    | EP RAD Storage Unit, Front View                          | 1-2  |

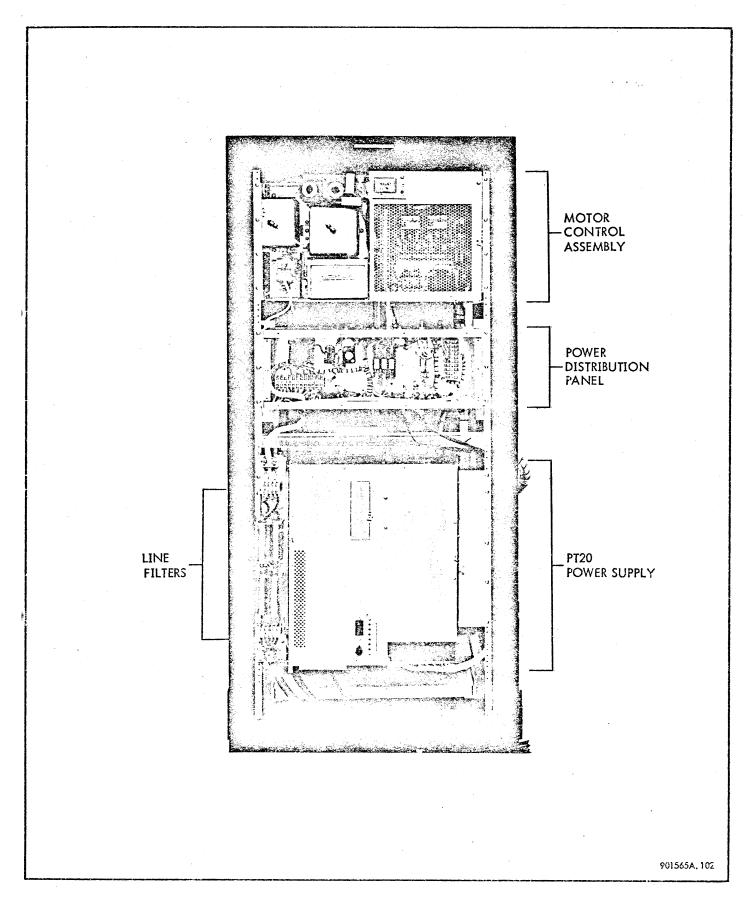

| 1-2    | EP RAD Storage Unit, Rear View                           | 1-3  |

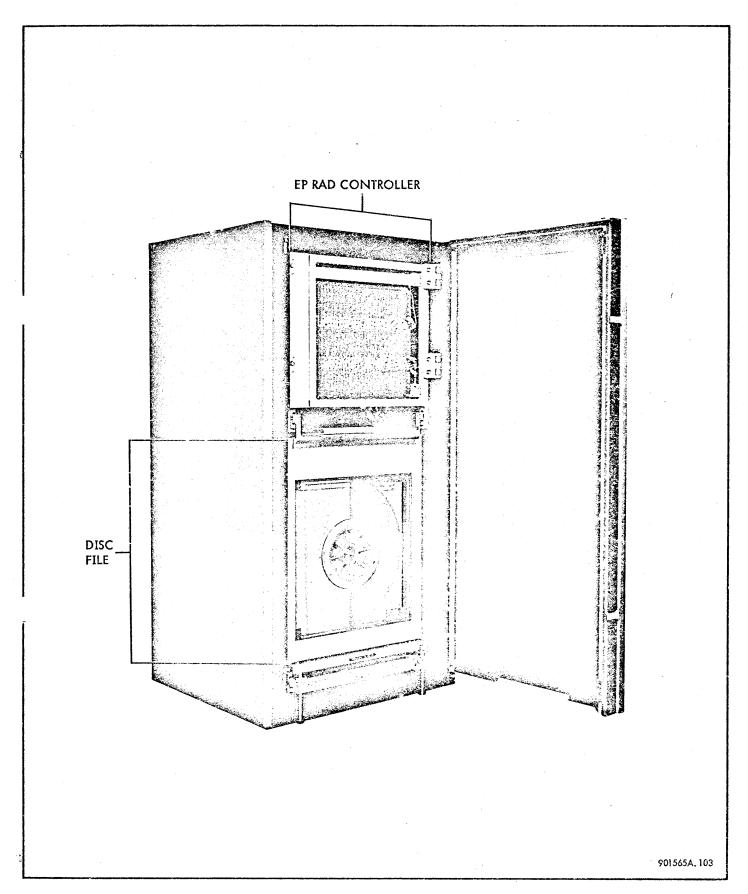

| 1-3    | EP RAD Storage Unit with EP RAD Controller, Front View   | ! -4 |

| 2-1    | LT26 Switch Comparator Module                            | 2-2  |

| 2-2    | LT25 Special Purpose Logic Module                        | 2-2  |

| 3-!    | E? RAD File, Black Diagram                               | 3-2  |

| 3-2    | FP RAD Disc File Data Organization                       | 3-3  |

| 3-3    | Response to IOP Commands, Flow Diagram                   | 3-5  |

| 3-4    | Seek Order Data Path, Block Diagram                      | 3-7  |

| 3-5    | Sense Order Data Path, Block Diagram                     | 3-8  |

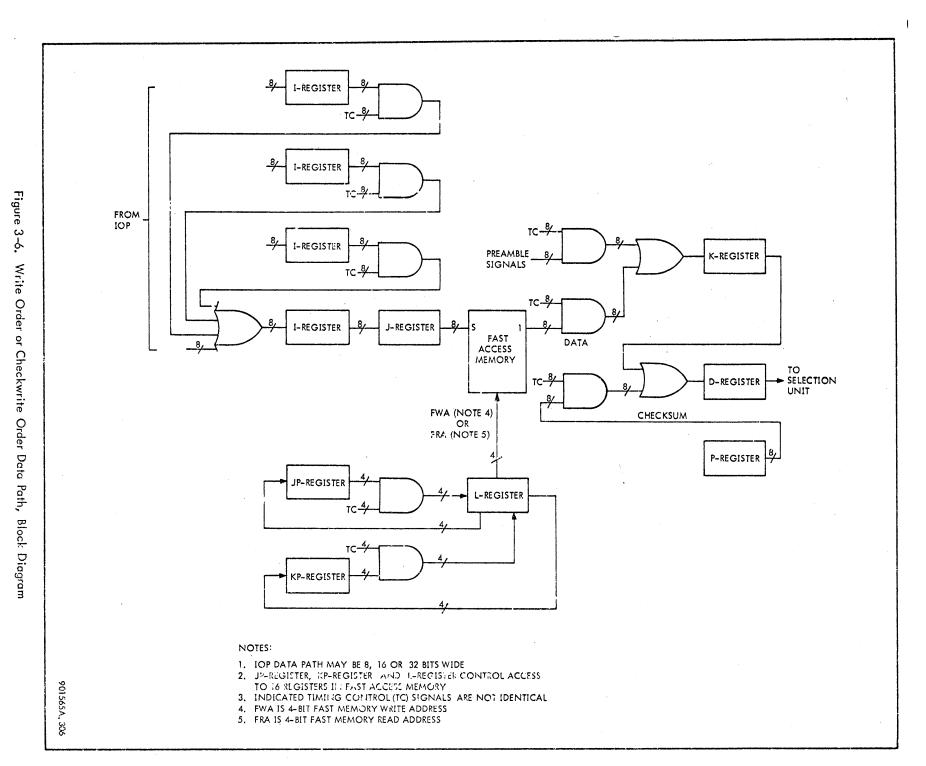

| 3-6    | Write Order or Checkwrite Order Data Path, Block Diagram | 3-9  |

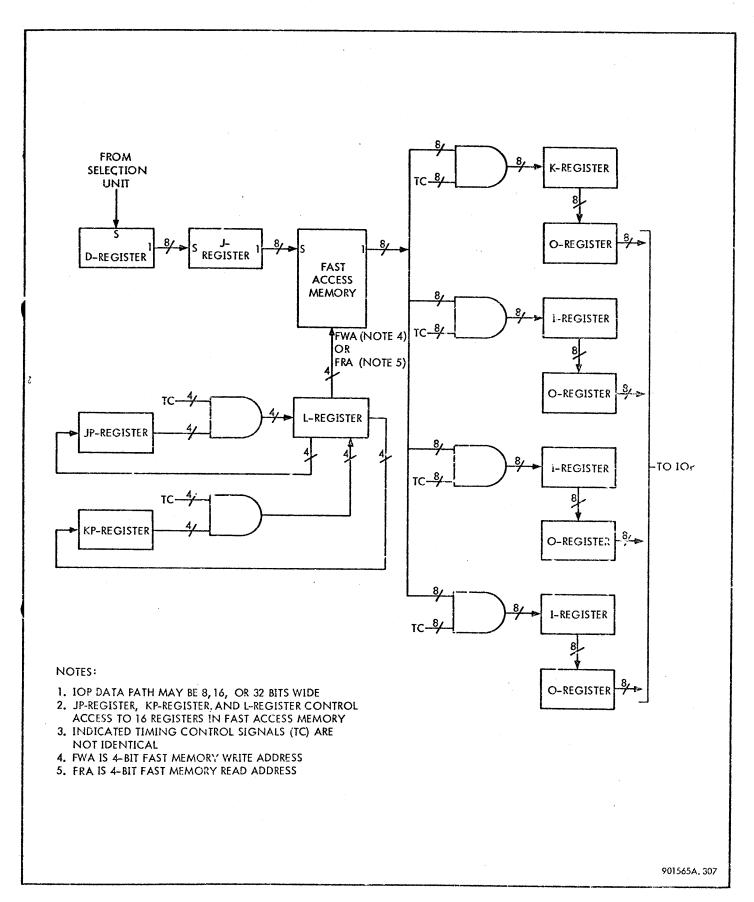

| 3-7    | Read Order Data Path, Block Digaram                      | 3-12 |

| 4-1    | Pneumatic System, Simplified Block Digaram               | 4-2  |

| 4-2    | Motor Control Assembly Start Sequence, Flow Diagram      | 4-4  |

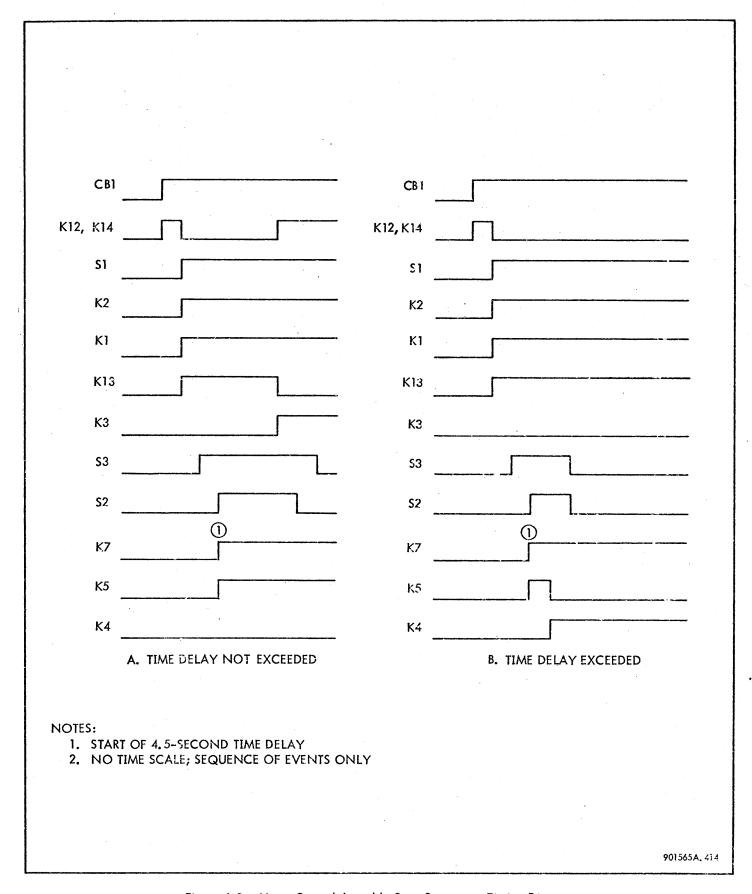

| 4-3    | Motor Control Assembly Start Sequence, Timing Diagram    | 4-5  |

| 4-4    | Motor Control Assembly Stop Sequence, Flow Diagram       | 4-6  |

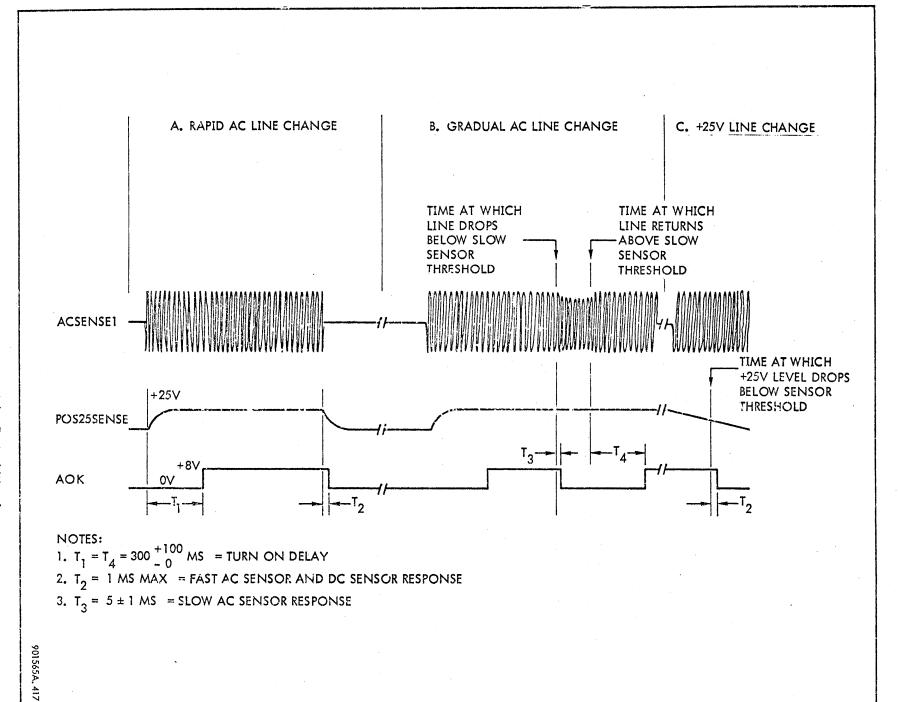

| 4-5    | WT29 Power Monitor Module, Typical Waveform              | 4-7  |

| 4-6    | Typical I/O Operations, Timing Diggram                   | 4-12 |

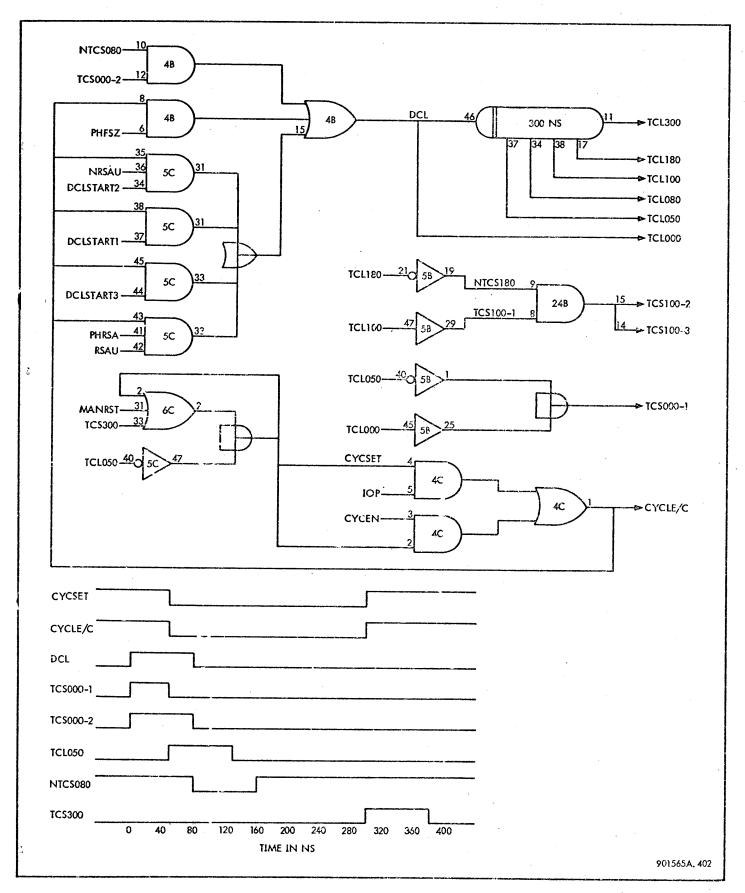

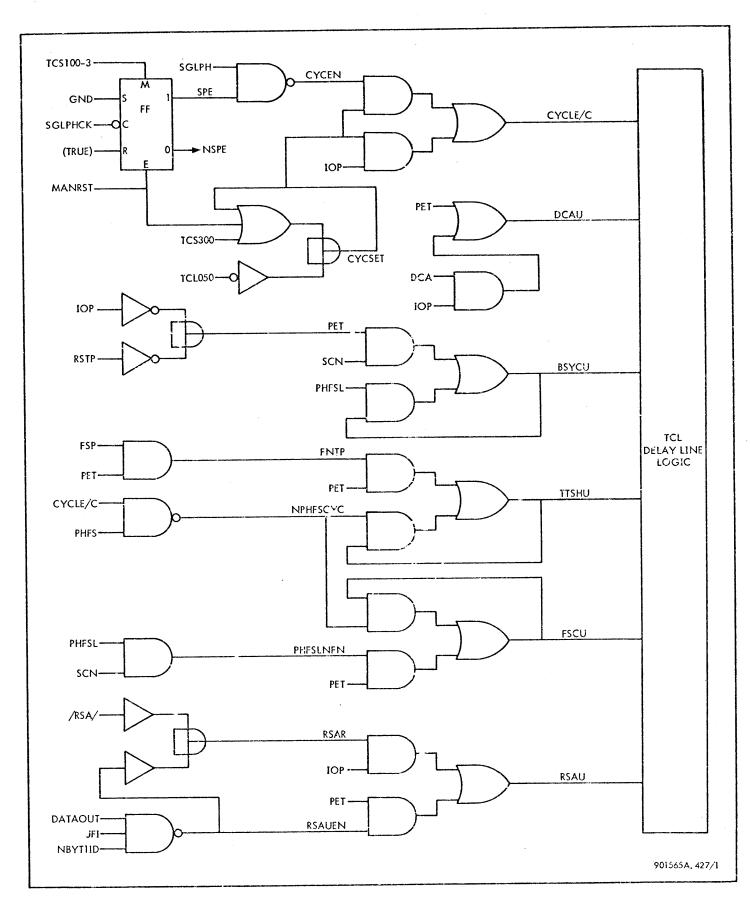

| 4-7    | TCL Delay Line. Timing and Logic Diagram                 | 4-14 |

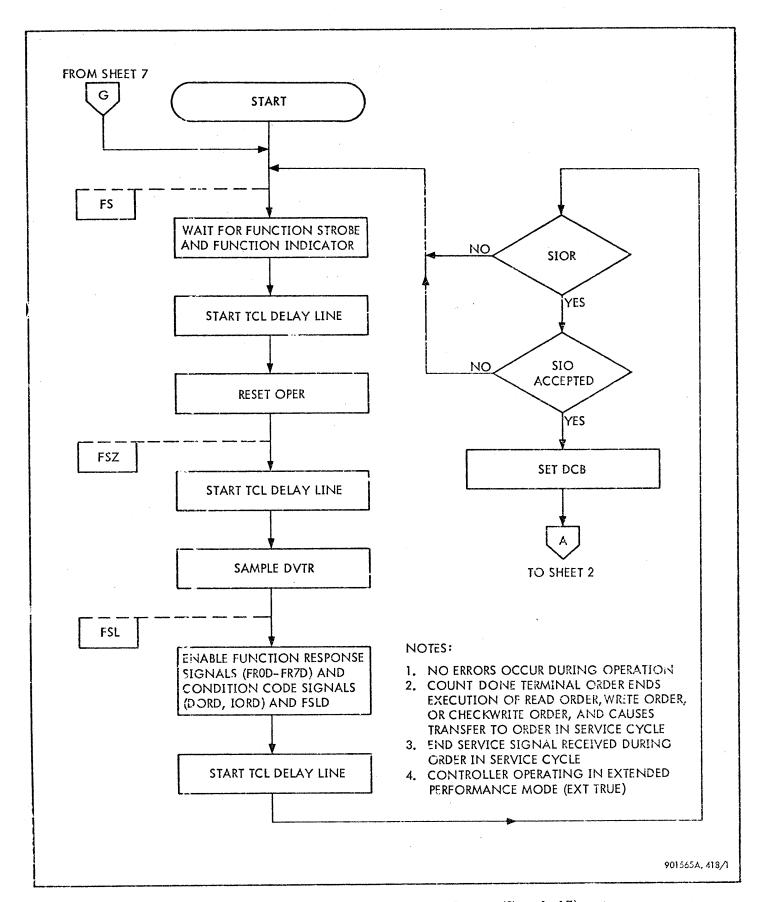

| 4-8    | Simplified Phase Sequence, Flow Diggram                  | 4-15 |

| 4-9    | Service Call Flip-Flop SCN. Logic Diagram                | 4-31 |

| 4-10   | End Data and End Service Logic, Logic Diagram            | 4-35 |

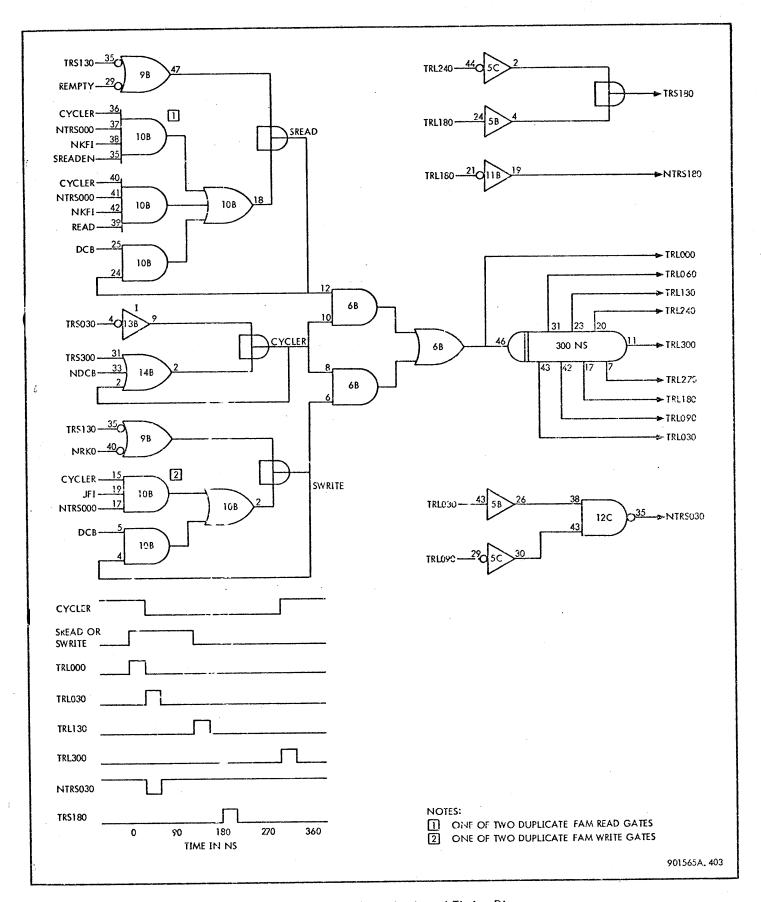

| 4-11   | FAM Circuits Simplified Logic Diggram                    | 4-42 |

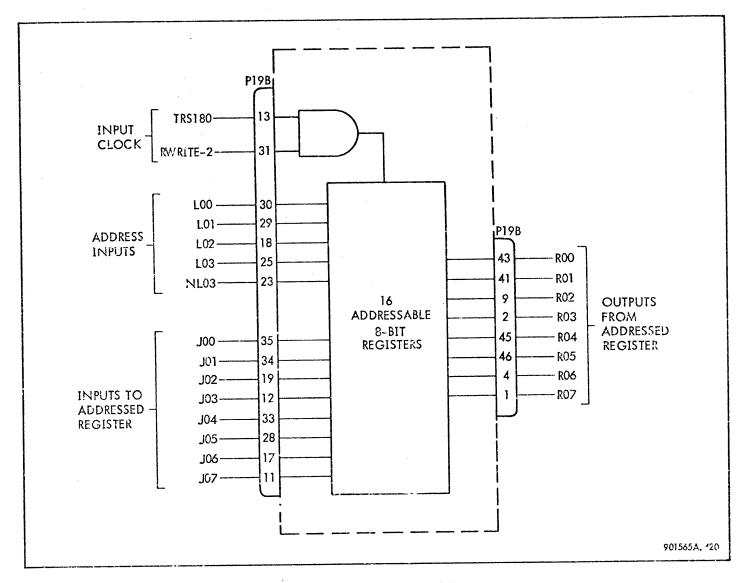

| 4-12   | FAM Module Block Diggram                                 | 4-43 |

| 4-13   | TRI Delay Line Logic and Timing Diggram                  | 4-44 |

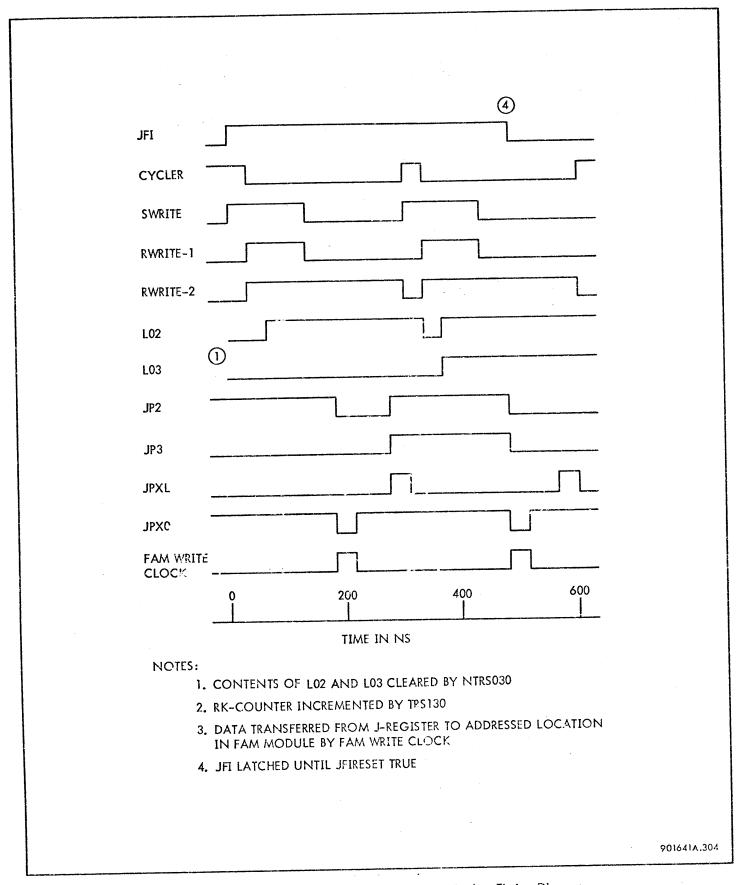

| 4-14   | Sequence of FAM Write Cycles, Timing Diagram             | 4-49 |

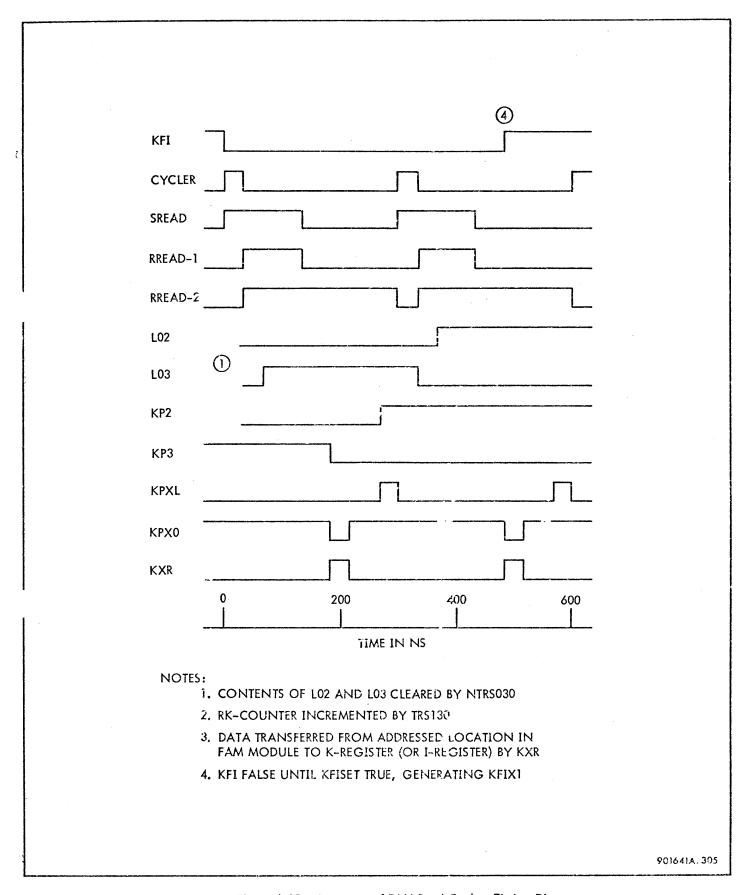

| 4-15   | Sequence of FAM Read Cycles, Timing Diagram              | 4-50 |

| 4-16   | TDL Delay Line, Logic and Timina Diagram                 | 4-59 |

| 4-17   | Track Shift Sequence, Timing Diagram                     | 4-66 |

# XDS 901565

# LIST OF ILLUSTRATIONS (Cont.)

| Figure           | Title                                                                             | Page         |

|------------------|-----------------------------------------------------------------------------------|--------------|

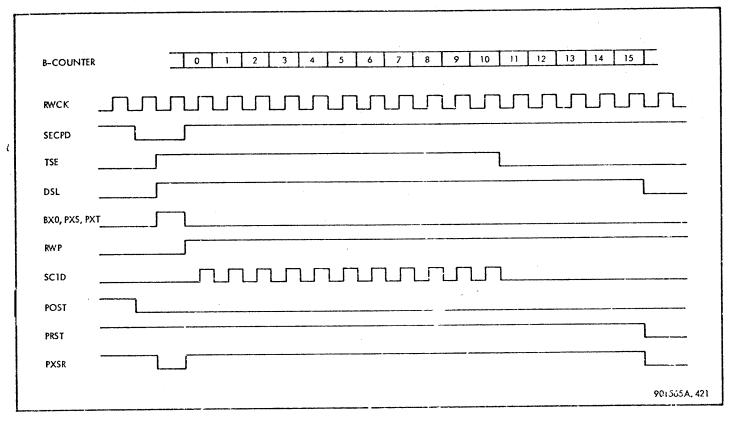

| 4-18             | Interface Control Circuits, Timing Diagram                                        | 4-67         |

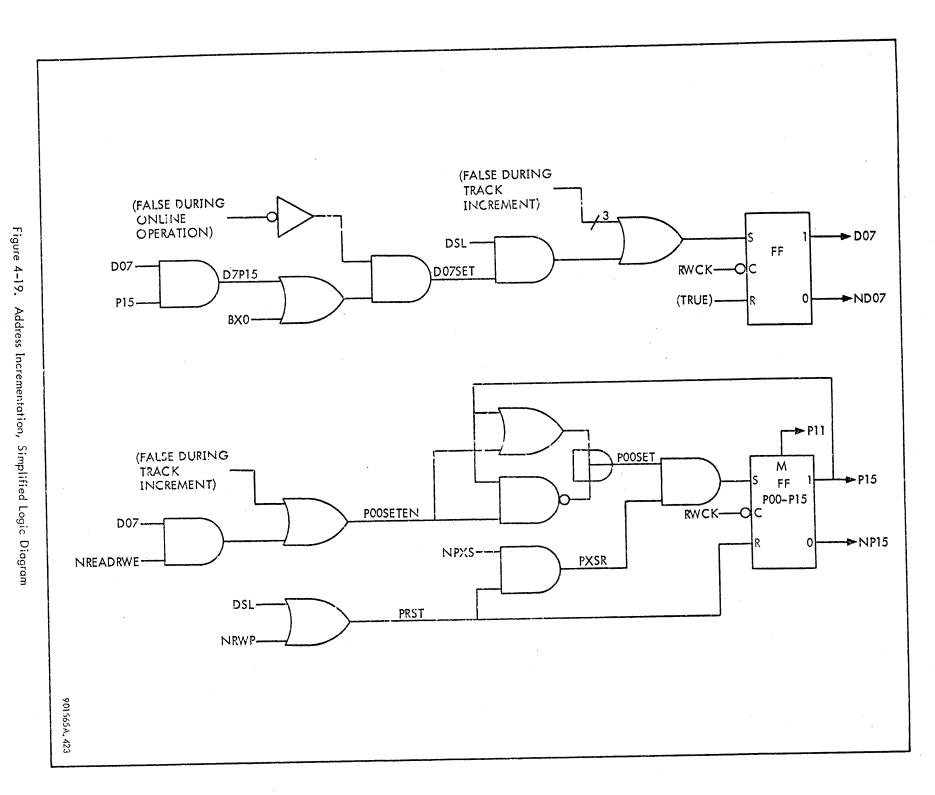

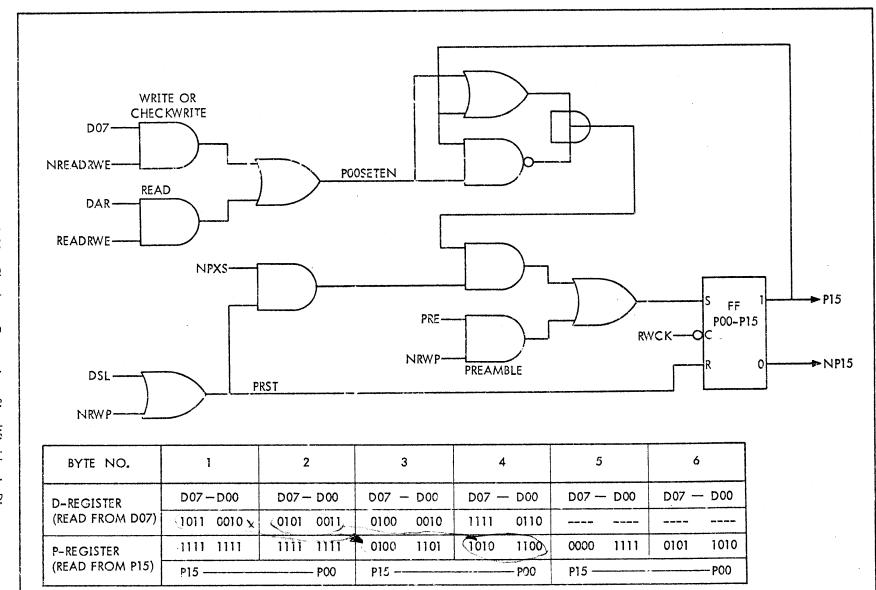

| 4-19             | Address Incrementation, Simplified Logic Diagram                                  | 4-73         |

| 4-20             | Checksum Generation, Simplified Logic Diagram                                     | 4-75         |

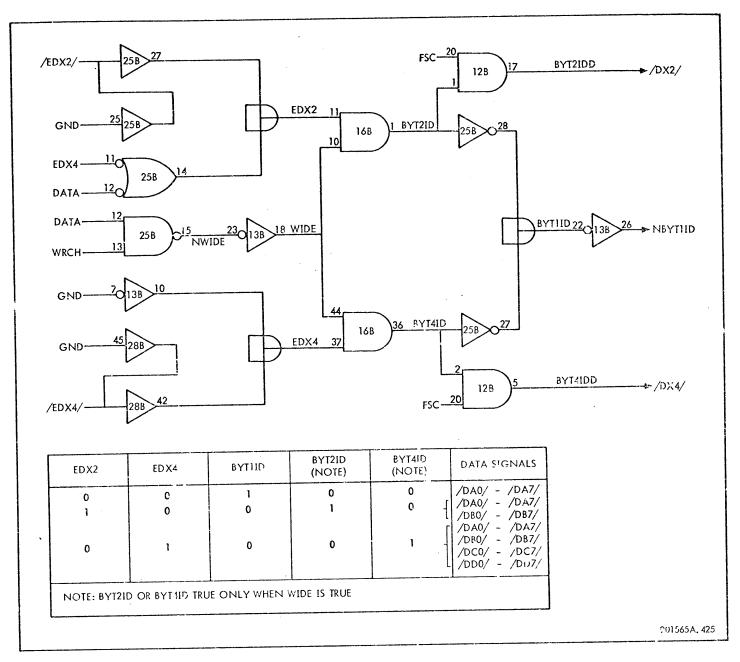

| 4-21             | Byte Width Circuits, Logic Diagram · · · · · · · · · · · · · · · · · · ·          | 4-81         |

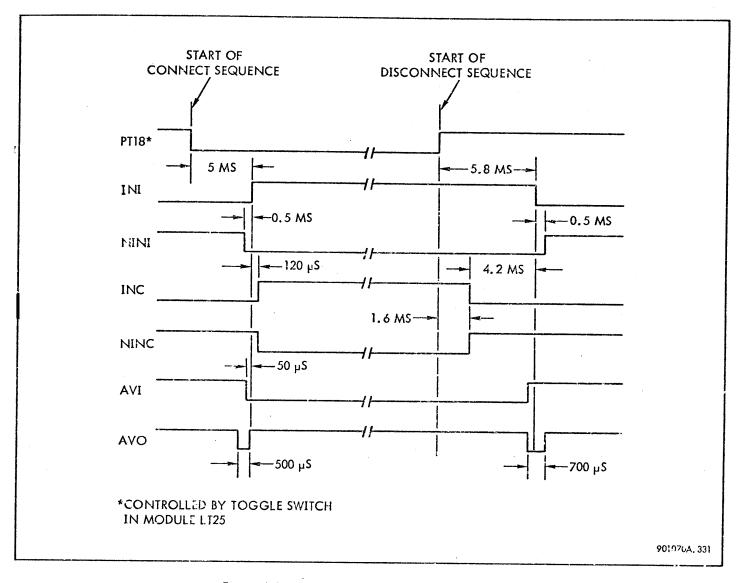

| 4-22             | Connect-Disconnect Timing Diagram                                                 | 4-82         |

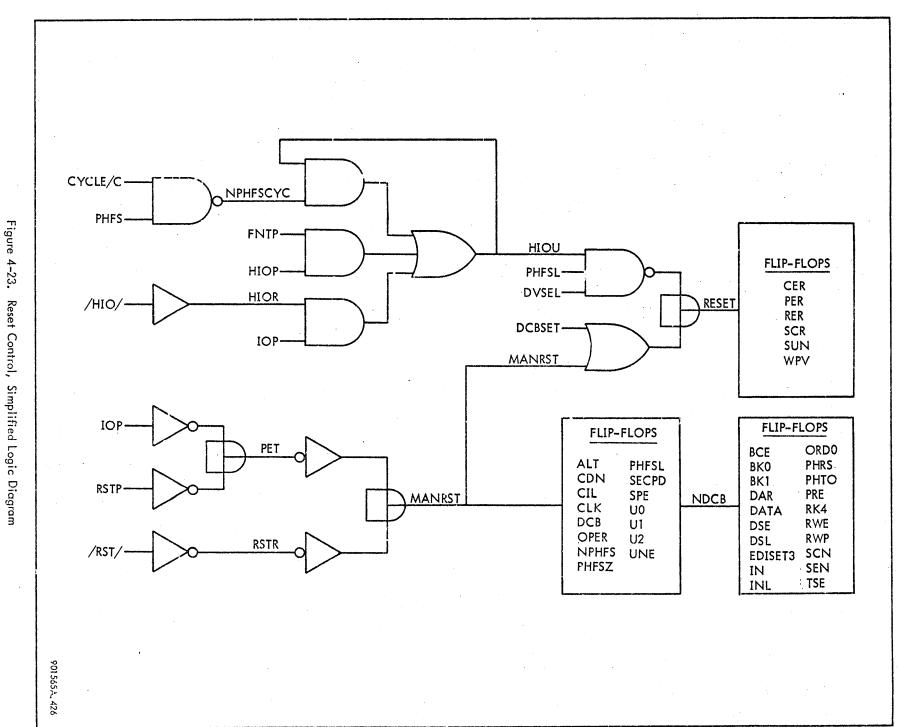

| 4-23             | Reset Control, Simplified Logic Diagram                                           | 4-83         |

| 4-24             | PET Interface Circuits, Simplified Logic Diagram                                  | 4-87         |

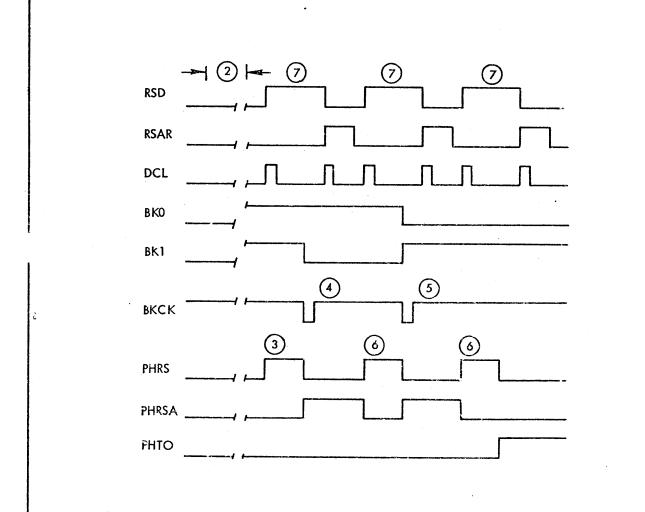

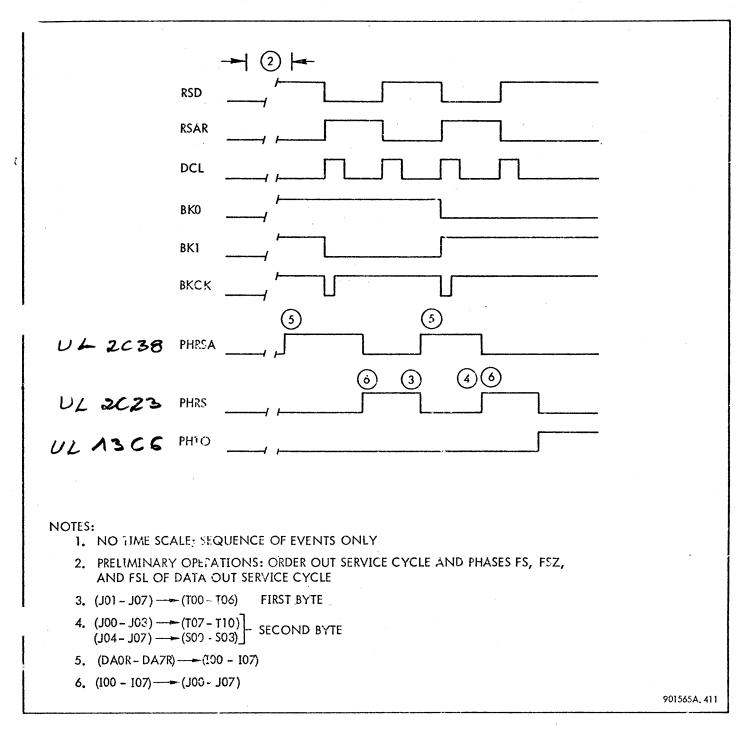

| 4-25             | Data Transfer During Sense Order, Timing Diagram                                  | 4-110        |

| 4-26             | Data Transfer During Seek Order, Timing Diagram                                   | 4-114        |

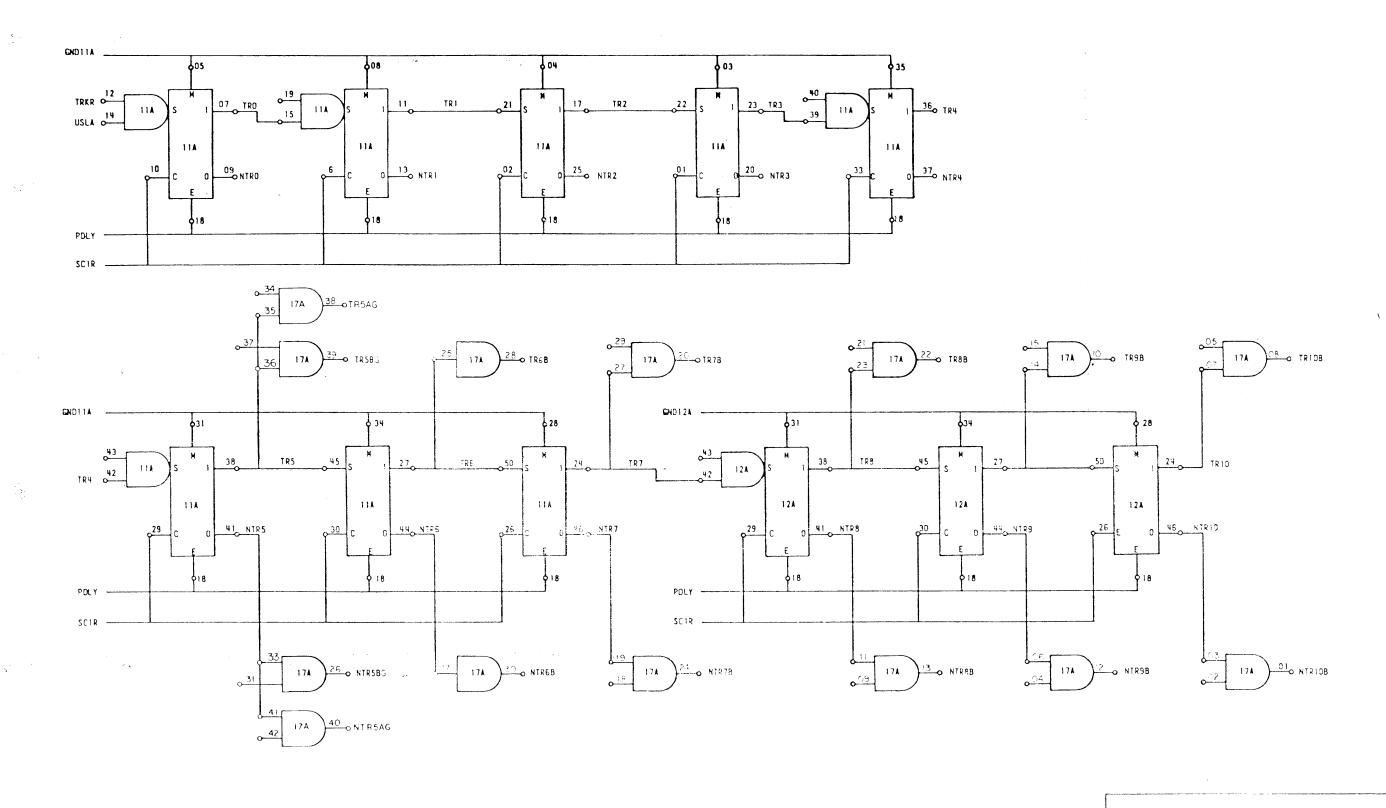

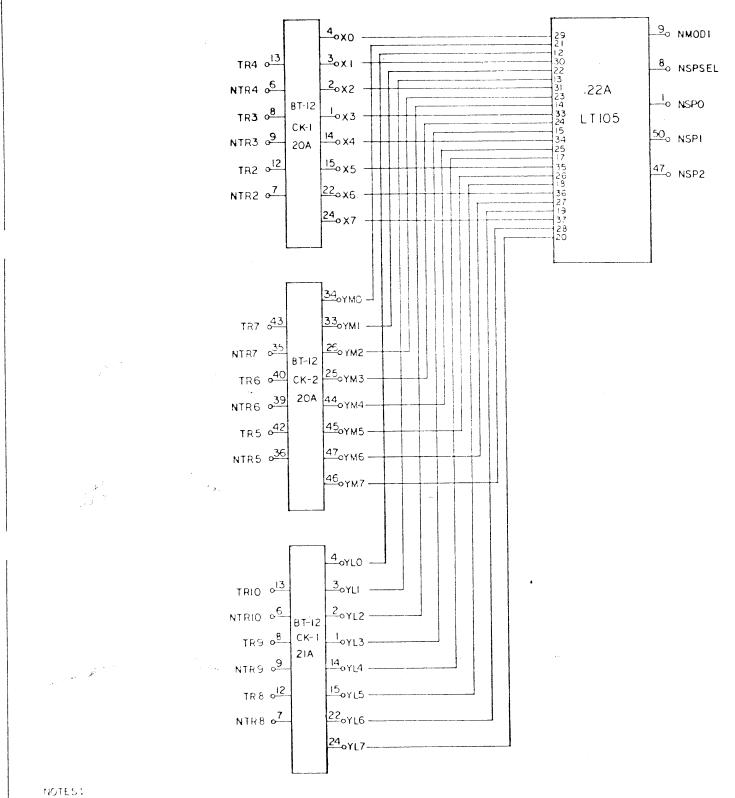

| 4-27             | Head Selection Matrix, Simplified Block Diagram                                   | 413          |

| 4-28             | Write Channel, Schematic Diagram                                                  | 4-139        |

| 4-29             | Part of Head Selection Matrix (Track 221), Schematic Diagram                      | 4-140        |

| 4-30             | Write Signals, Timing Diagram                                                     | 4-14         |

|                  | Read Channel, Schematic Diagram                                                   | 4-143        |

| 4-02             | Read Signals, Timing Diagram                                                      | 4-145        |

| 4-33             | Logical Sparing Circuits, Block Diagram                                           | 4-148        |

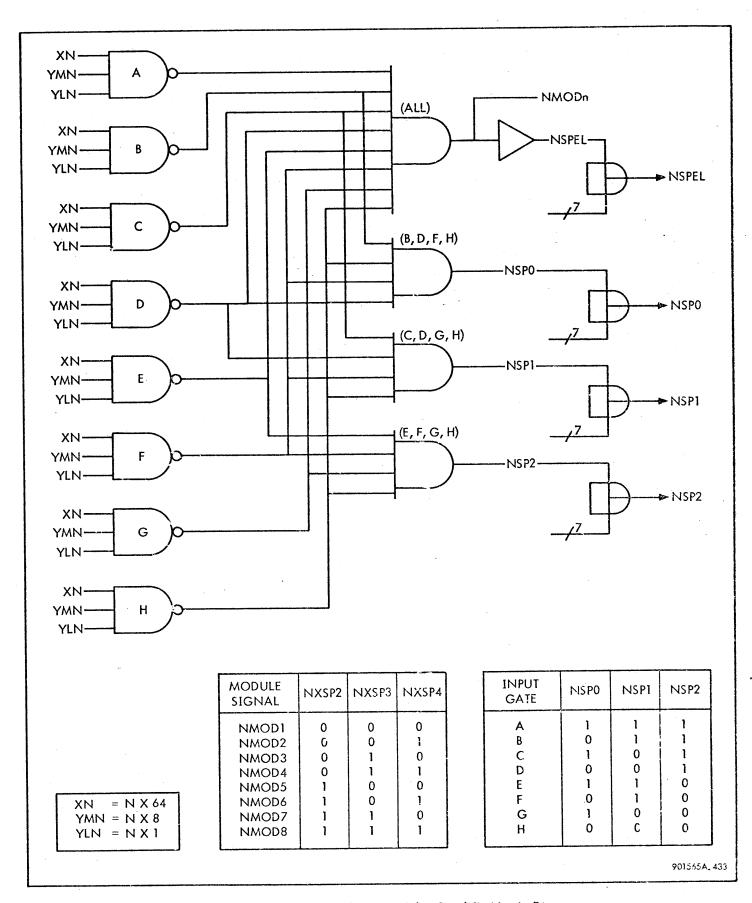

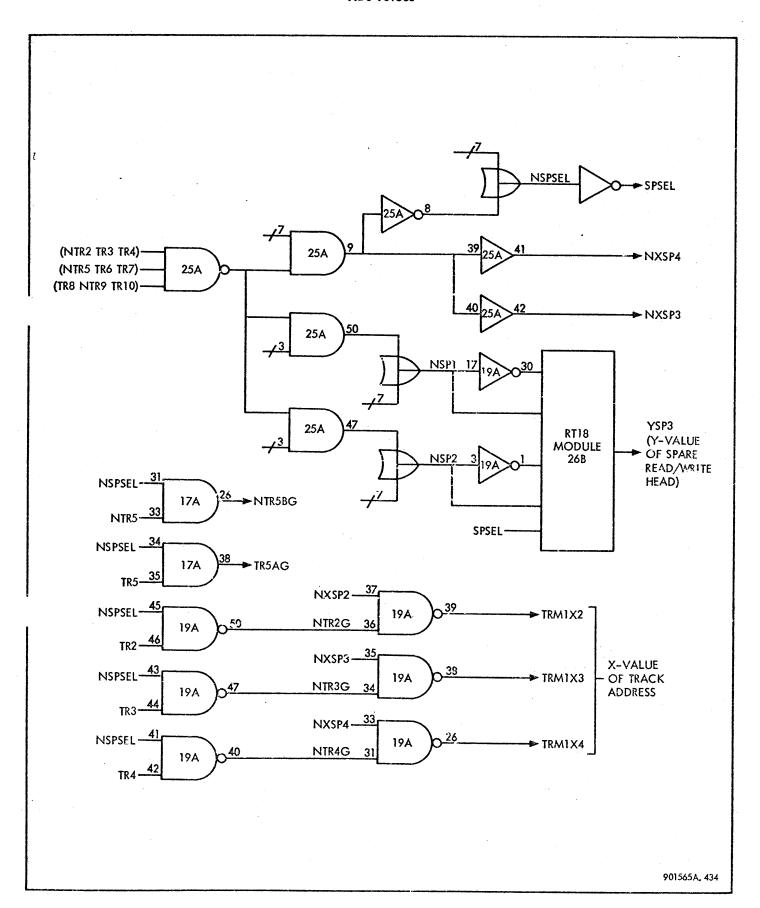

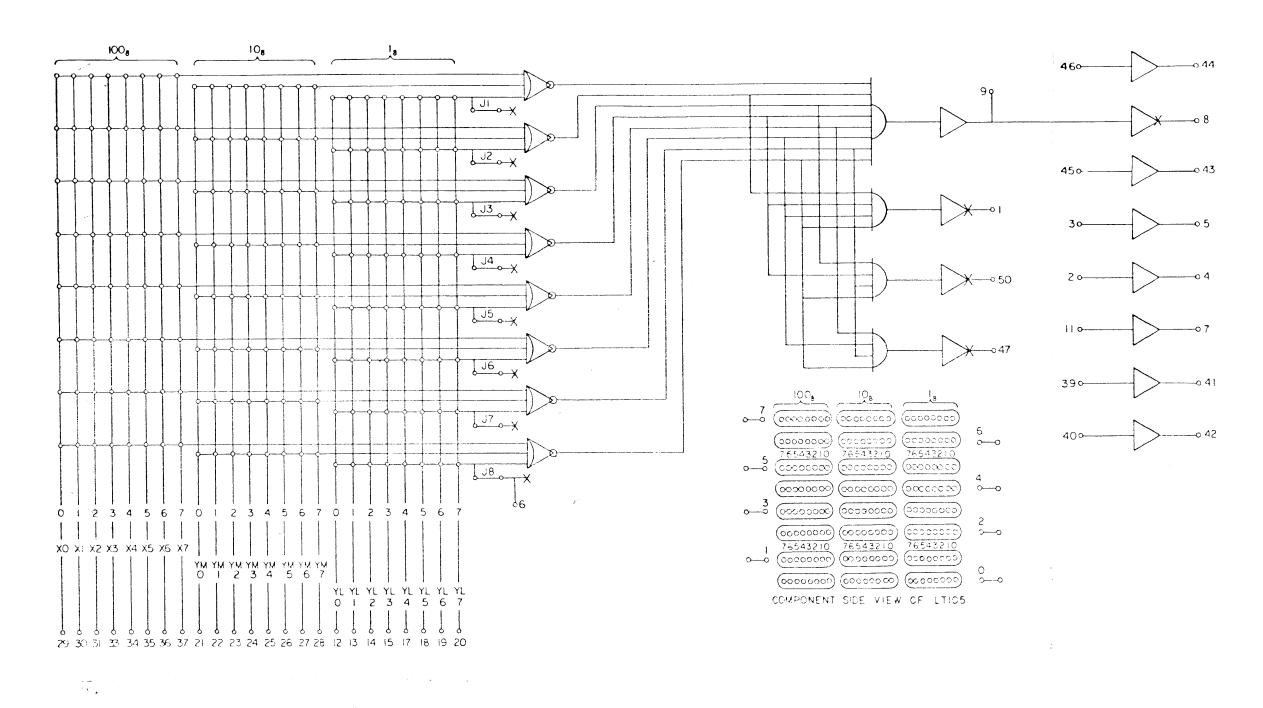

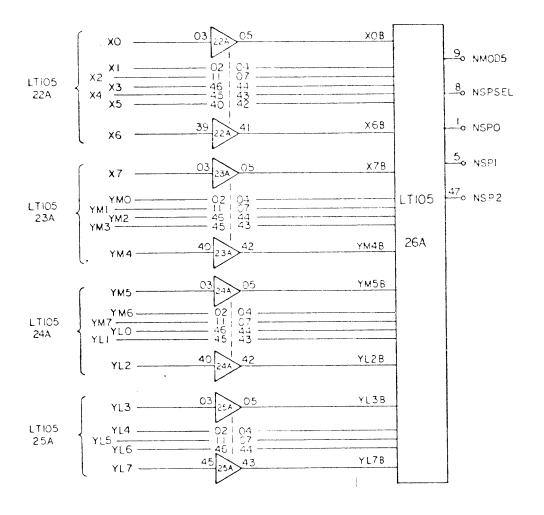

| 4-34             | LT105 Spares Selector Module, Simplified Logic Diagram                            | 4-149        |

| 4-35             | Logical Sporing Circuits for Track 221 (Octal 335), Simplified Logic Diagram      | 4-150        |

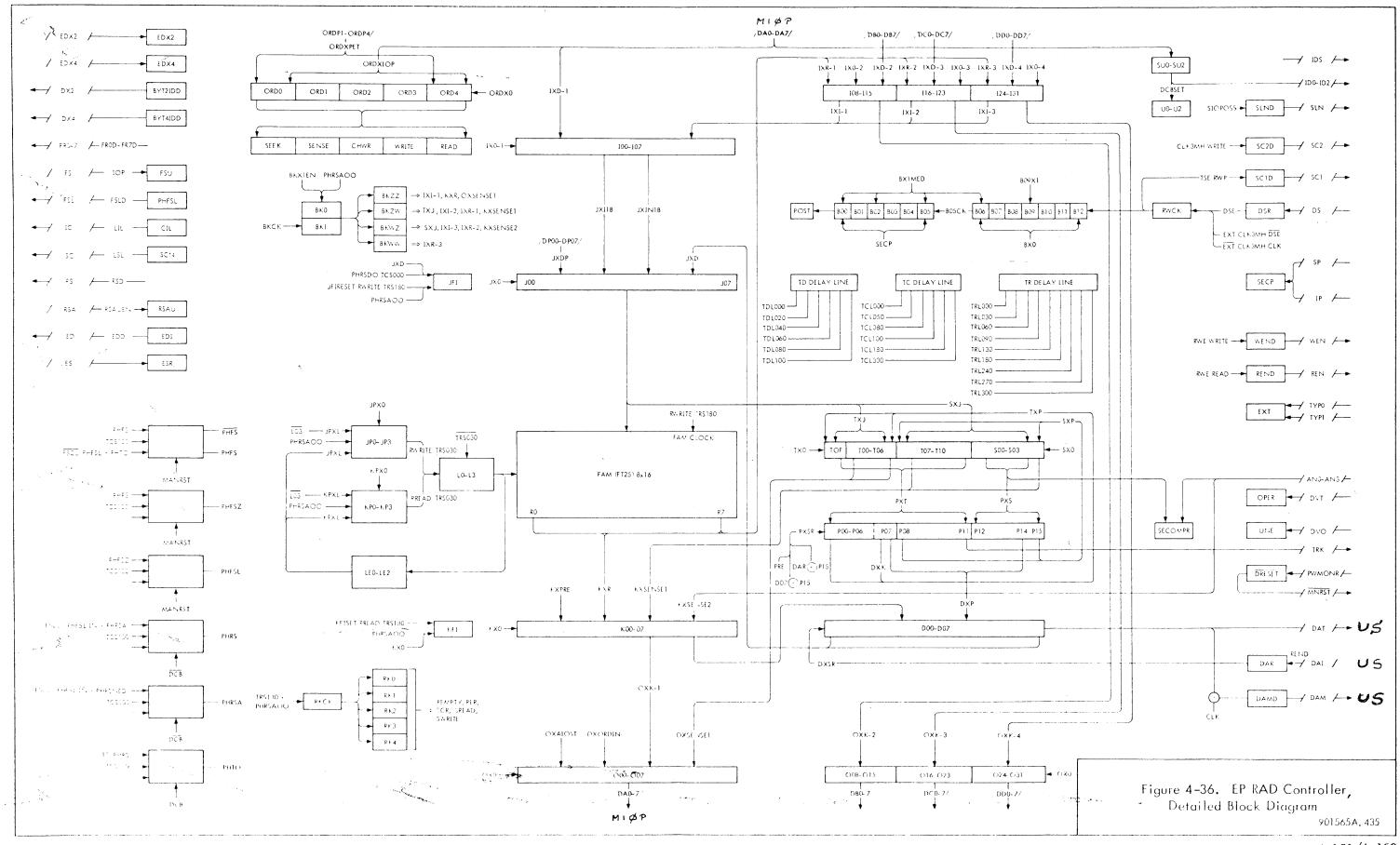

| 4-36             | EP RAD Controller, Detailed Block Diagram                                         | 4-15         |

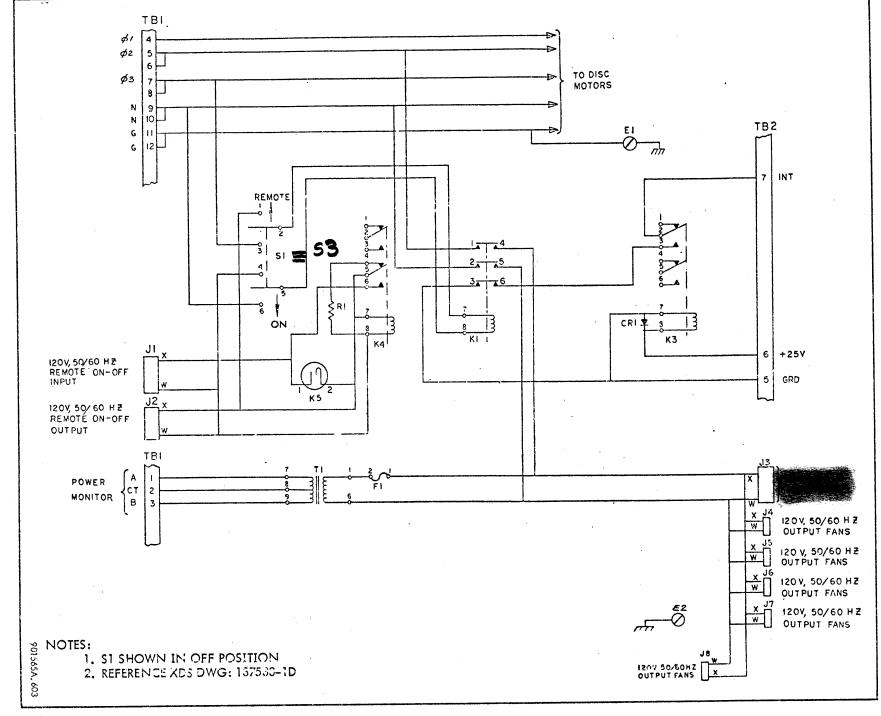

| 6-1              | Power Distribution Panel, Schematic Diagram                                       | 6-2          |

| 6-2              | EP RAD Selection Unit, Power Distribution, Chassis Wiring Diagram                 | 6-3          |

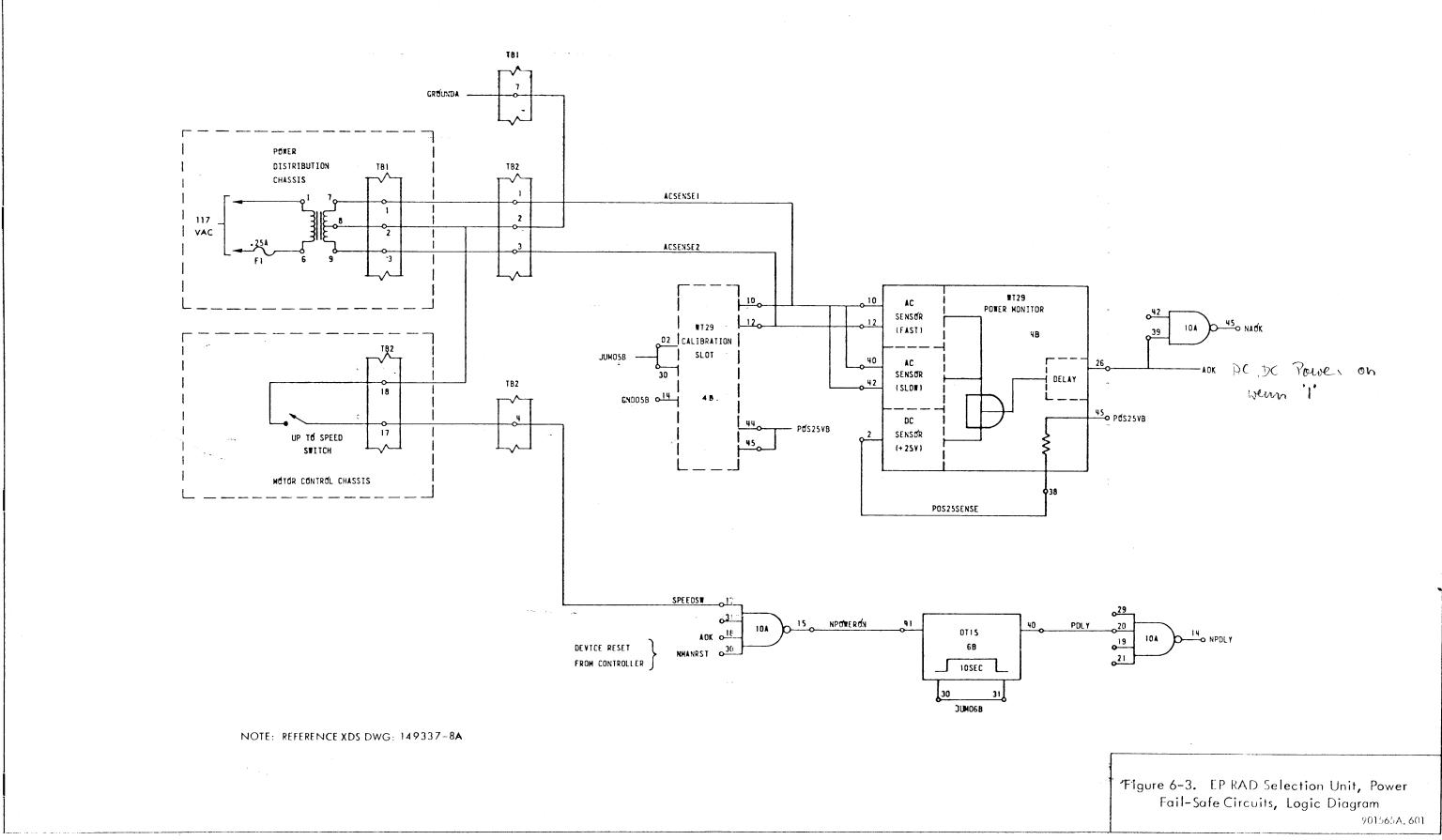

| 6-3              | EP RAD Selection Unit, Power Fail-Safe Circuits, Logic Diagram                    | 6-5          |

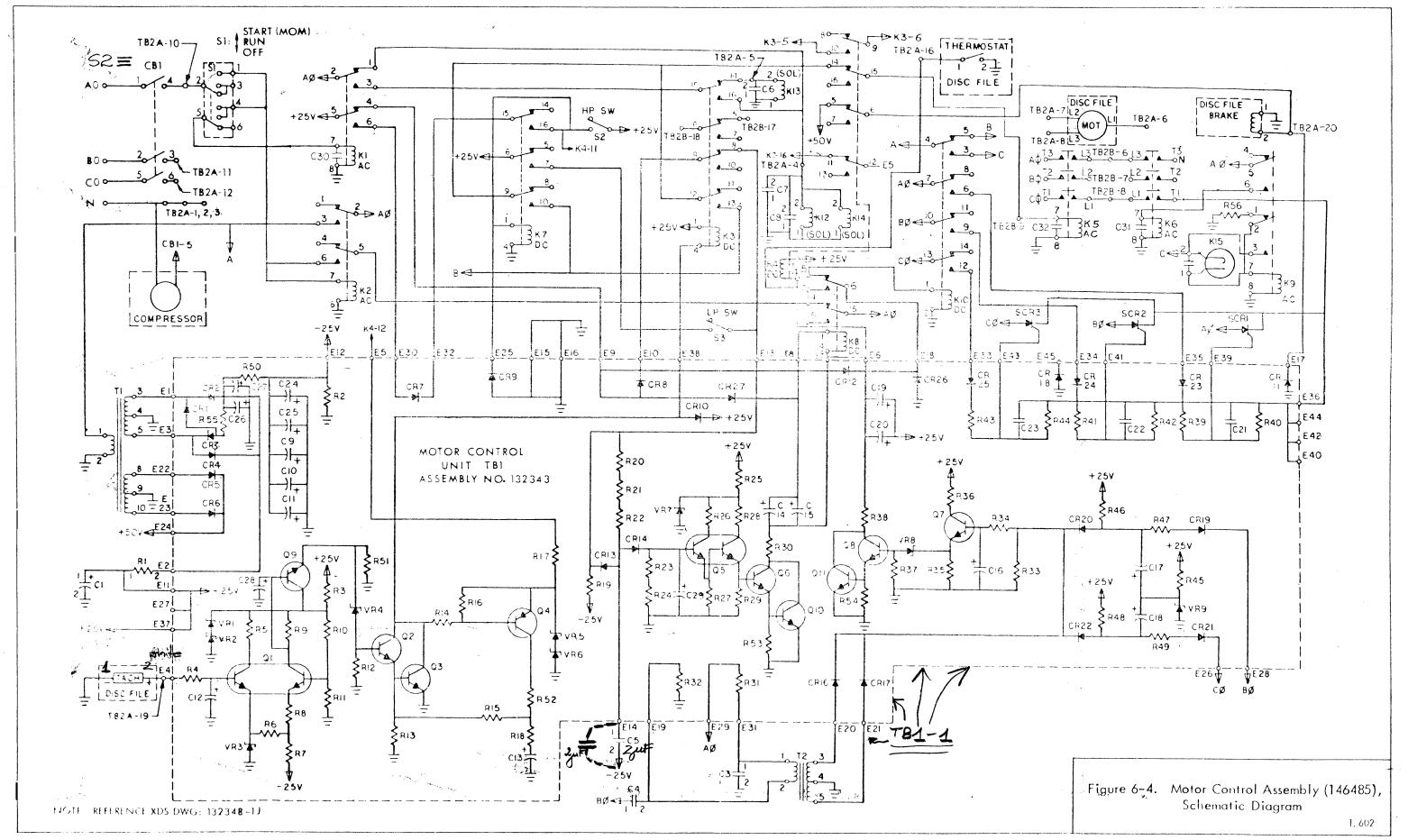

| 6-4              | Motor Control Assembly (146485), Schematic Diagram                                | 6-6          |

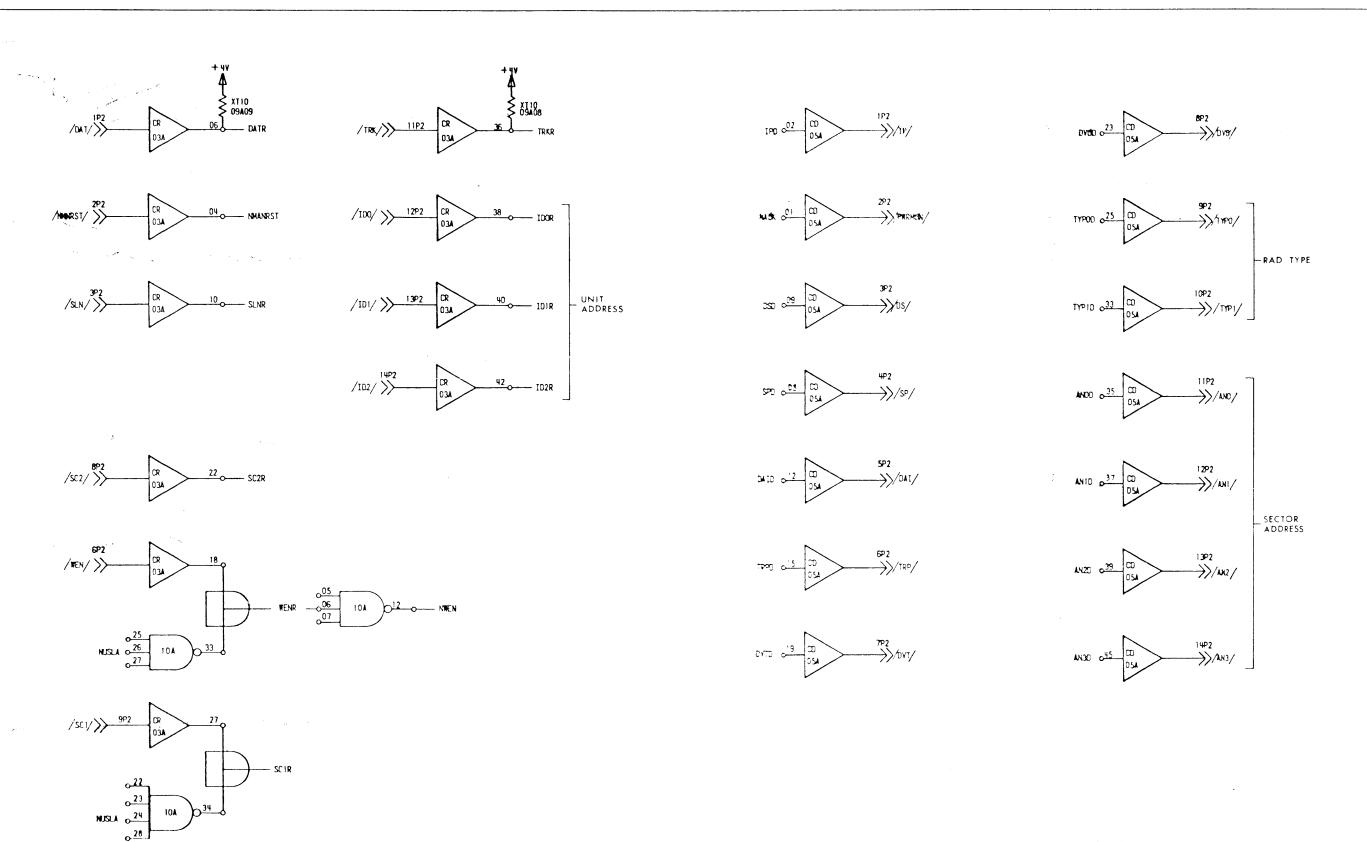

| 6-5              | EP KAD Selection Unit, Address Circuits, Logic Diagram                            | 6-7          |

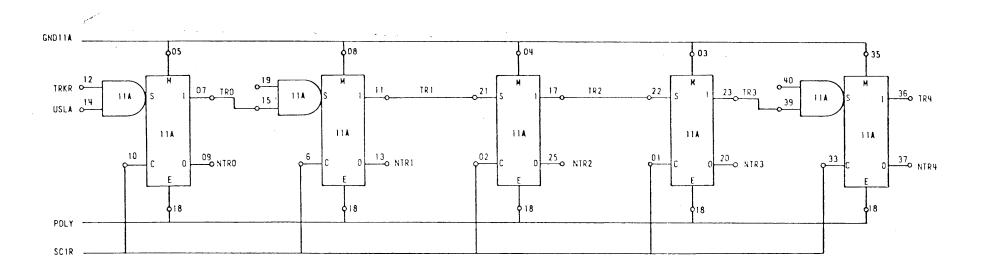

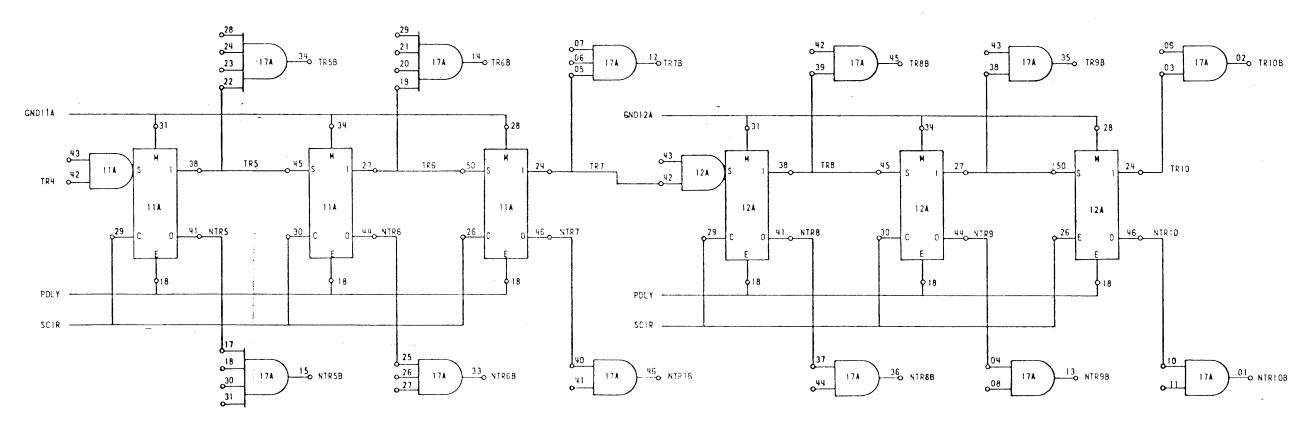

| 6-6              | Er KAD Selection Unit, Track Register (Without Logical Sparing), Logic Diagram    | ó-9          |

| 6-7              | EP KAD Selection Unit, Input/Output Circuits, Logic Diggram                       | 6-10         |

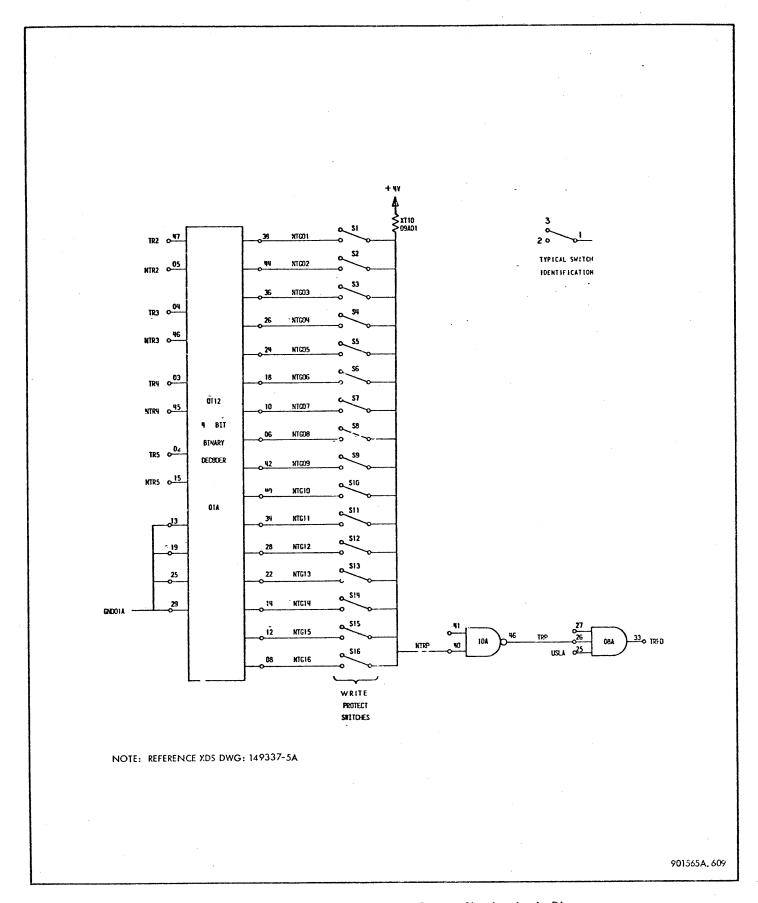

| <b>6-8</b>       | Er KAD Selection Unit, Memory Protect Circuits, Logic Diagram                     | 6-11         |

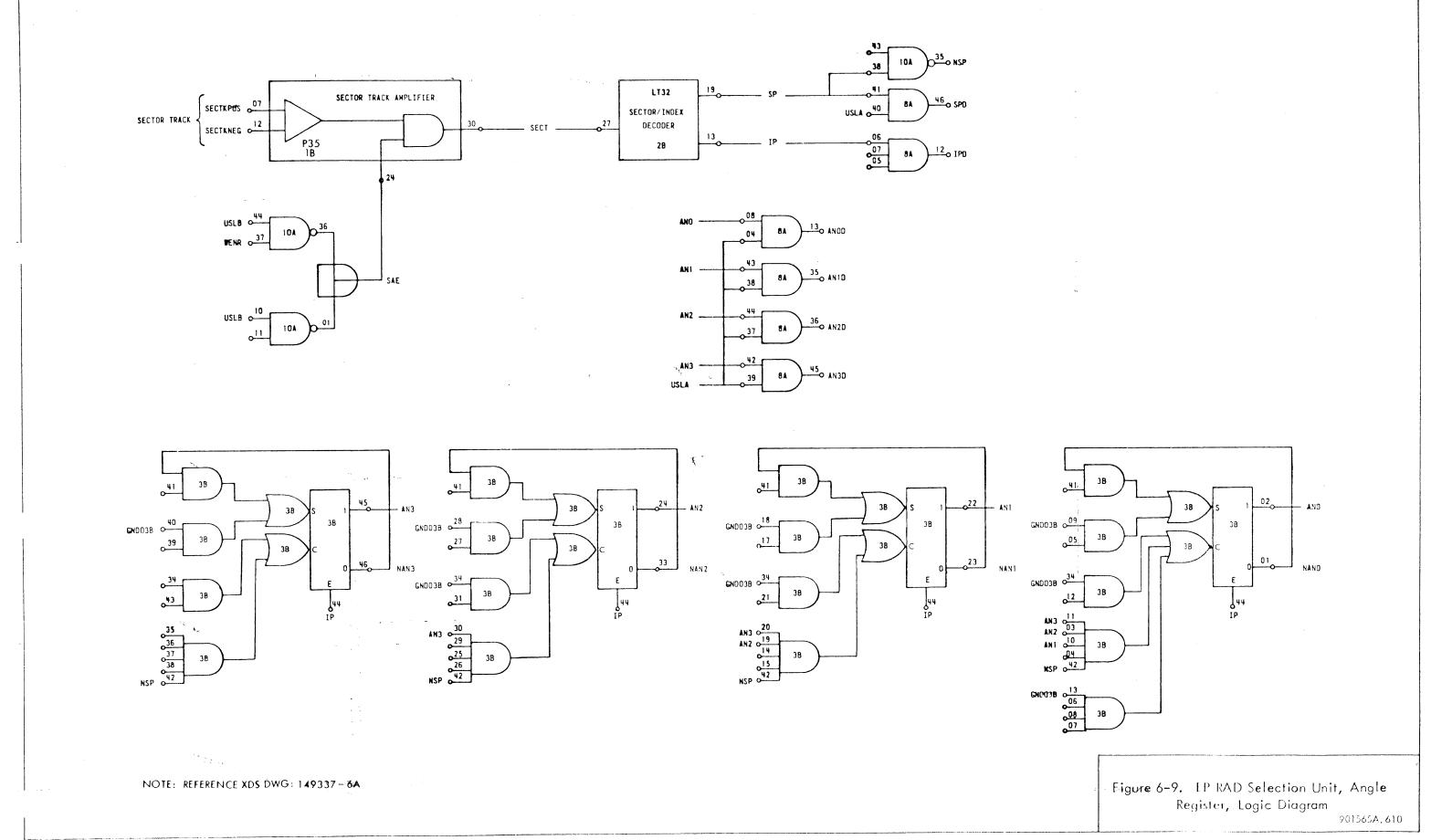

| 6-9              | Er KAD Selection Unit. Angle Register, Logic Diagram                              | 6-13         |

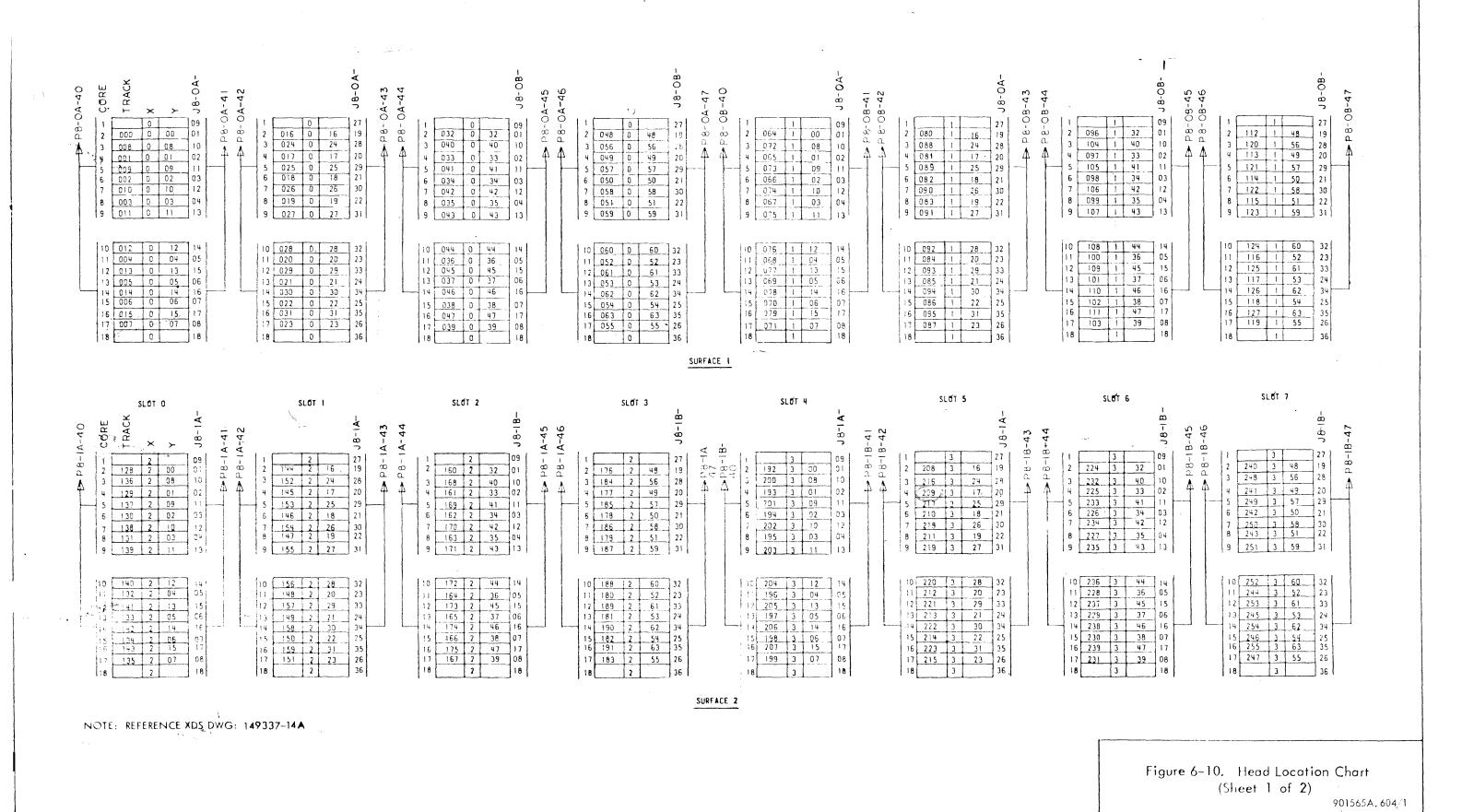

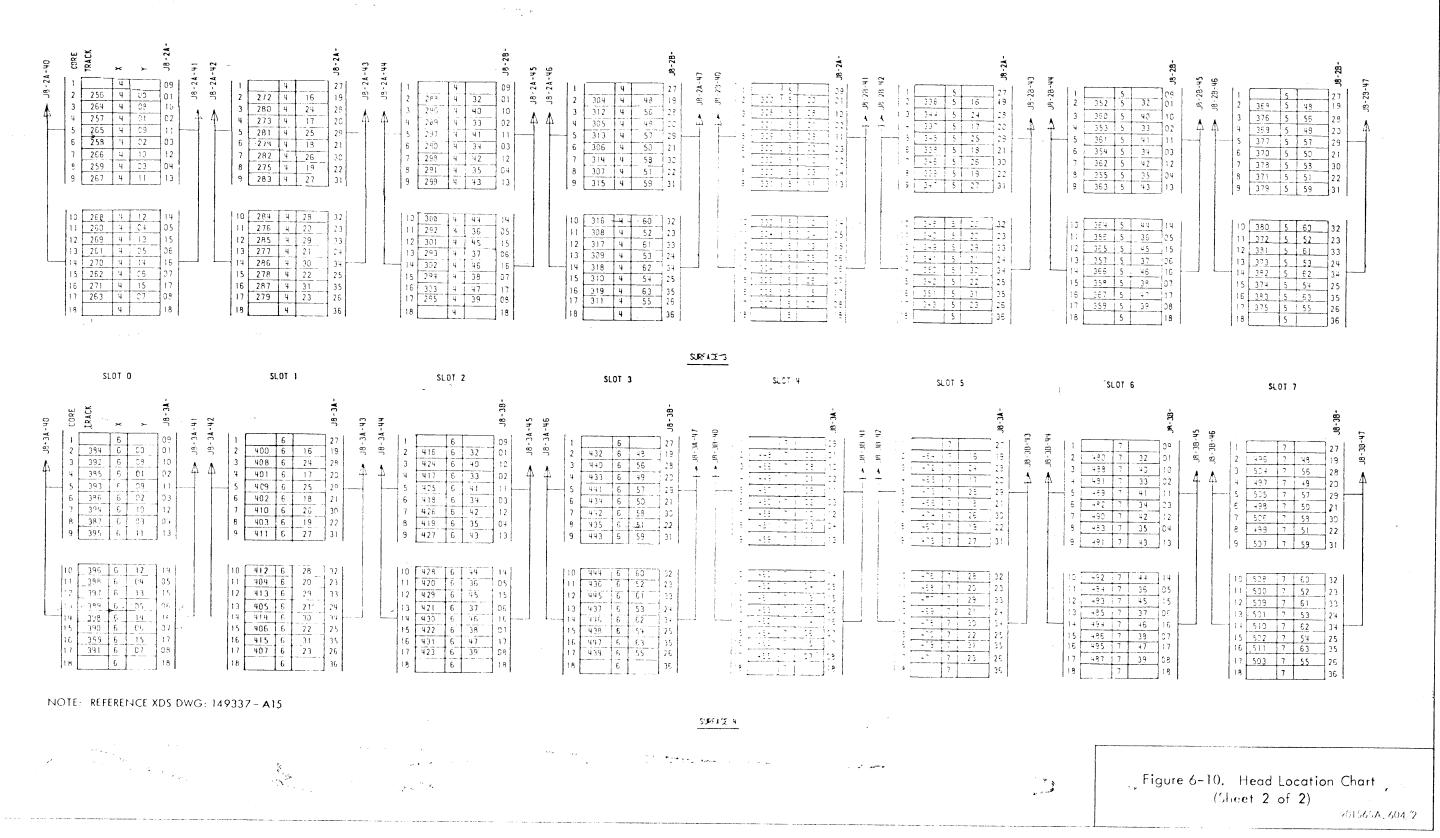

| 6-10             | Head Location Chart                                                               | 0-14         |

| 6-11             | nead Centertap Chart                                                              | 6-17         |

| 6-12             | Y-Select Location Chart (Without Logical Sparing)                                 | 6-18         |

| 6-13             | Input/Output and Start/Finish Location Chart (Without Logical Sparing)            | 6-19         |

| 6-14             | Motor Control Assembly (152692), Schematic Diagram                                | 6-21         |

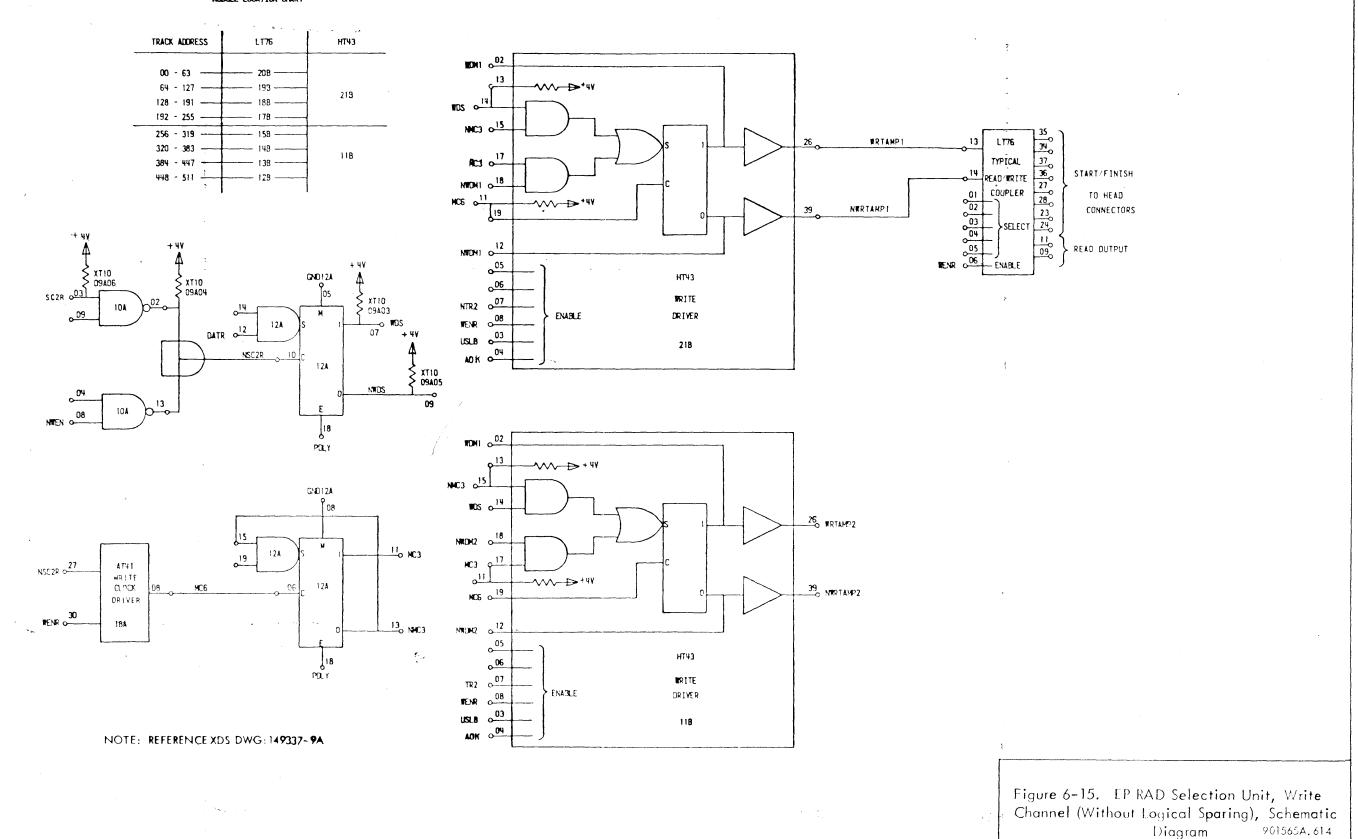

|                  | EP RAD Selection Unit, Write Channel (Without Logical Sparing), Schematic Diagram | 6-22         |

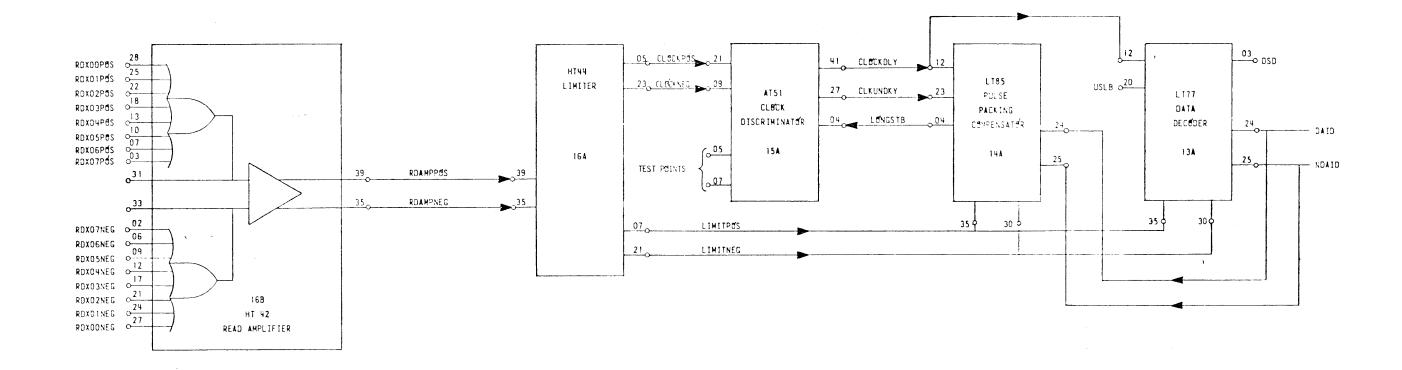

| (17)             | EP RAD Selection Unit, Read Channel, Schematic Diagram                            | 6-23         |

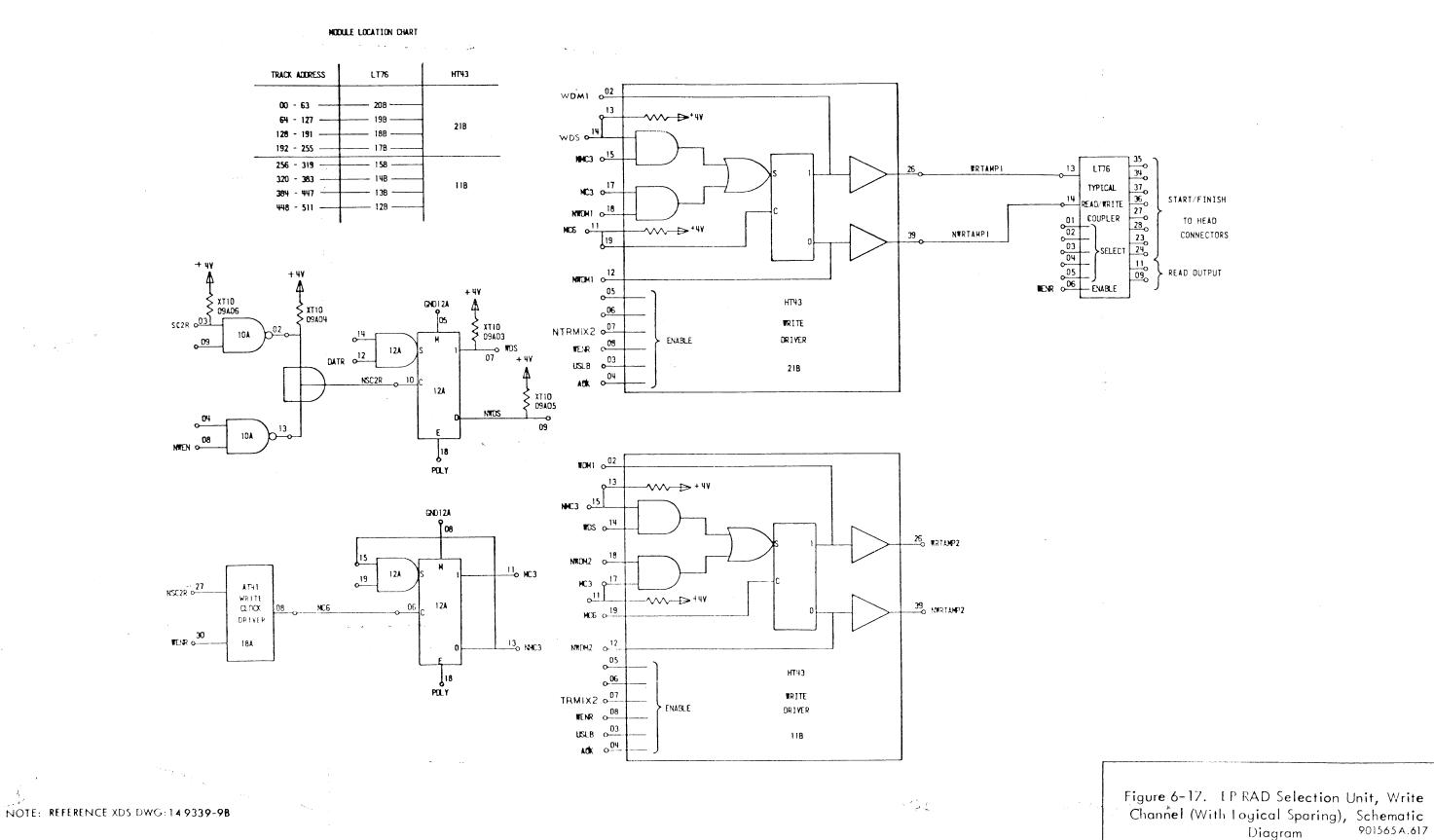

| 6-17             | EP RAD Selection Unit, Write Channel (With Logical Sparing), Schematic Diagram    | 5 -24        |

| 6-18             | EP RAD Selection Unit, Track Register (With Logical Sparing), Schematic Diagram   | ა́-25        |

| 6-19             | Input/Output and Start/Finish Location Chart (With Logical Sparing)               |              |

| 6-20             | Y-Select Location Chart (With Logical Sparing)                                    | <b>ú27</b>   |

| 6-21             | LT105 Spares Selector Module, Logic Diagram                                       | 6-28         |

| 6-22<br>7-1      | EP KAD Selection Unit, Spares Select Circuits, Logic Diagram                      | <b>3-2</b> 9 |

|                  | EP RAD Storage Unit, Installation Drawing                                         | 7-7          |

| 7-2<br>7-3       | EP RAD File, Cabling Diagram                                                      | 7_3          |

| 7-3<br>7-4       | EP RAD Controller, Cable Connections                                              | 7-11         |

| 7-4<br>7-5       | EP RAD Selection Unit, Module Location Chart                                      | 7-12         |

|                  | EP RAD Controller, Module Location Chart                                          | 7-13         |

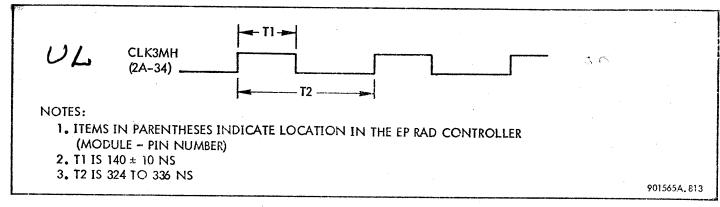

| 8-1              | Signal CLK3MH, Timing Diagram                                                     | 8-3          |

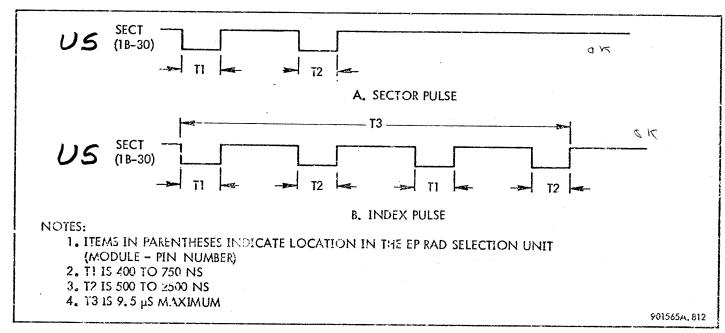

| 8-2              | Signal SECT, Timing Diagram                                                       | 8-3          |

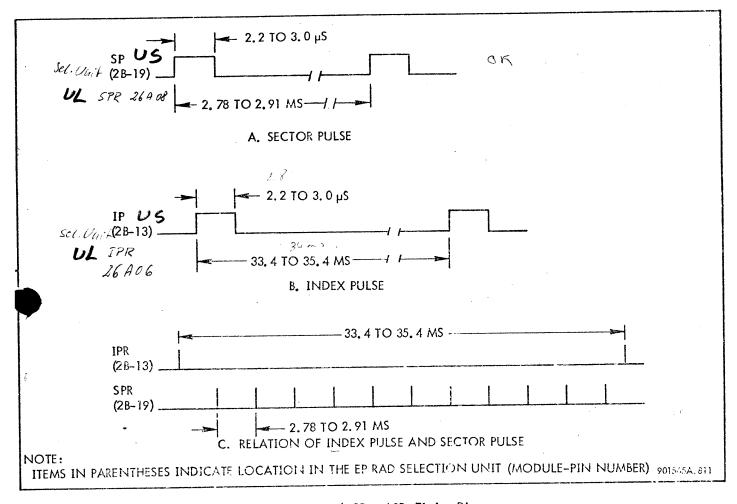

| 8-3              | Signals SP and IP, Timing Diagram                                                 | 8-4          |

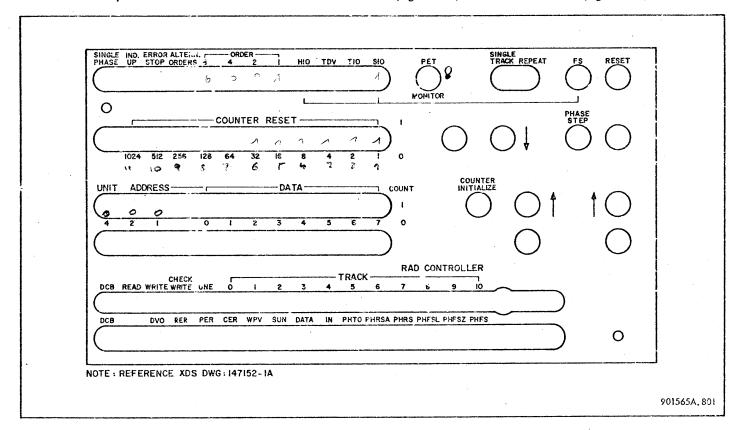

| 8-4              | PET Panel Overlay                                                                 | 8-5          |

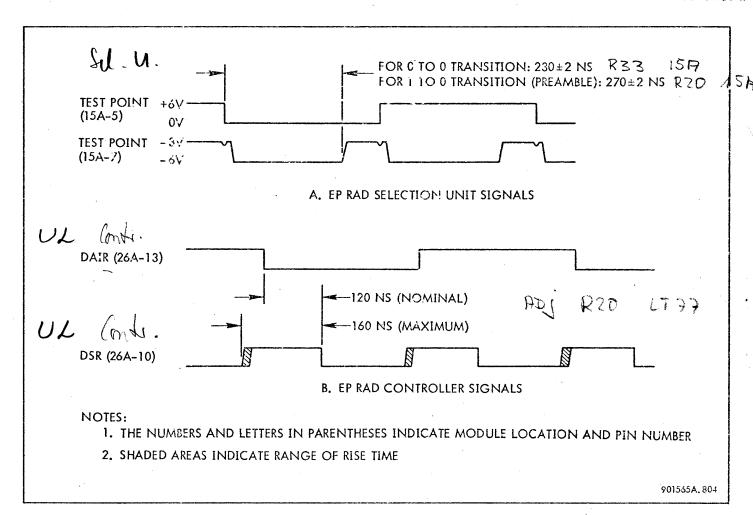

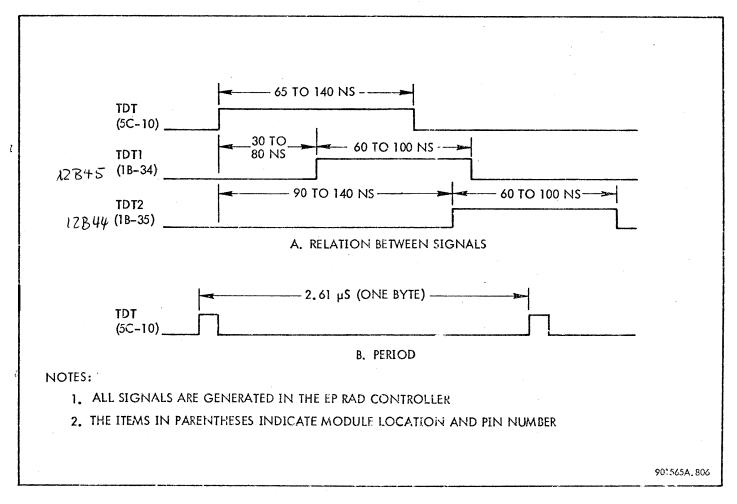

| 8 <sub>უ</sub> 5 | Data Clock Signals, Timing Diagram                                                | 8-6          |

#### XDS 901565

# LIST OF ILLUSTRATIONS (Cont.)

| Figure | Title                                                    | Page |

|--------|----------------------------------------------------------|------|

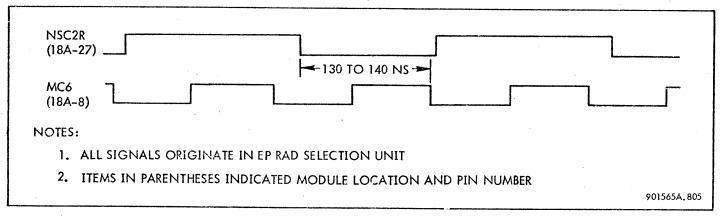

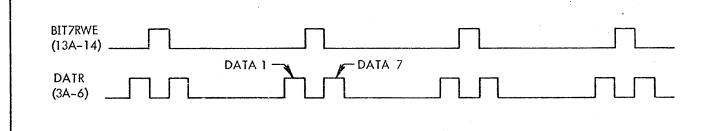

| 8-6    | Data Synchronization Signals, Timing Diagram             | 8-7  |

| 8-7    | Sector Identification Signals, Timing Diagram            | 8-13 |

| 8-8    | TDL Delay Line Signals, Timing Diagram                   | 8-14 |

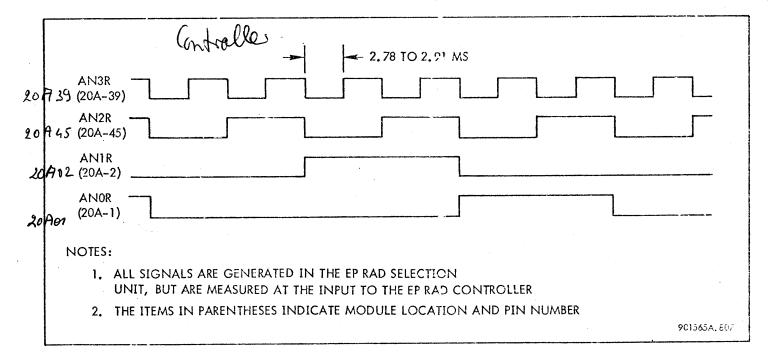

| 8-9    | Head Select Signals, Timing Diagram                      | 8-16 |

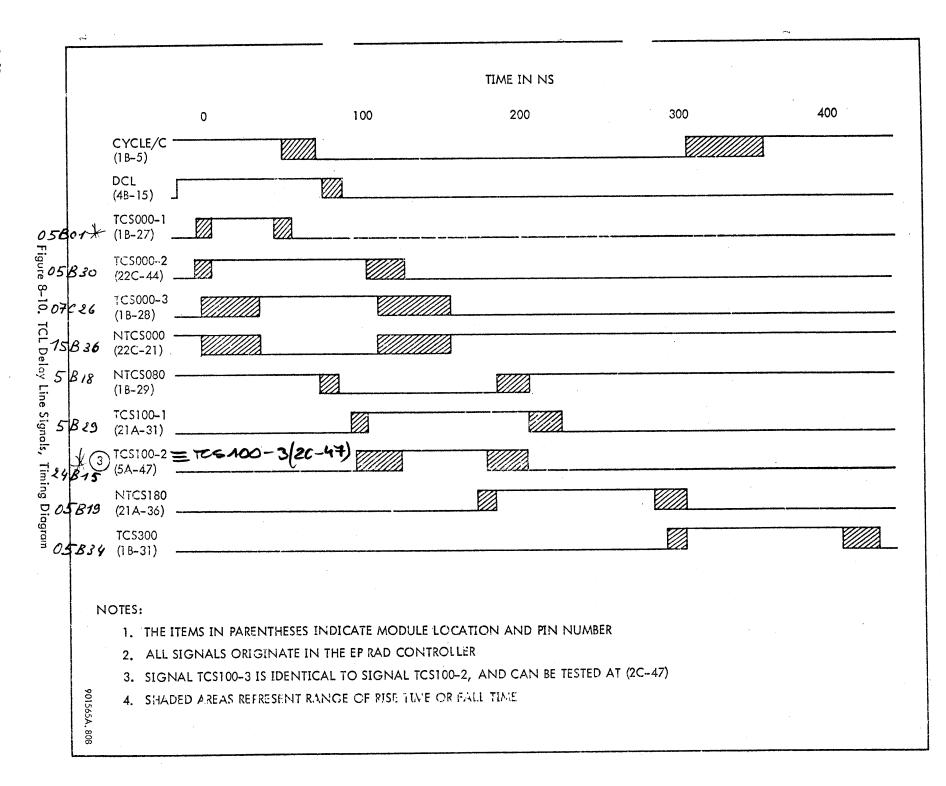

| 8-10   | TCL Delay Line Signals, Timing Diagram                   | 8-18 |

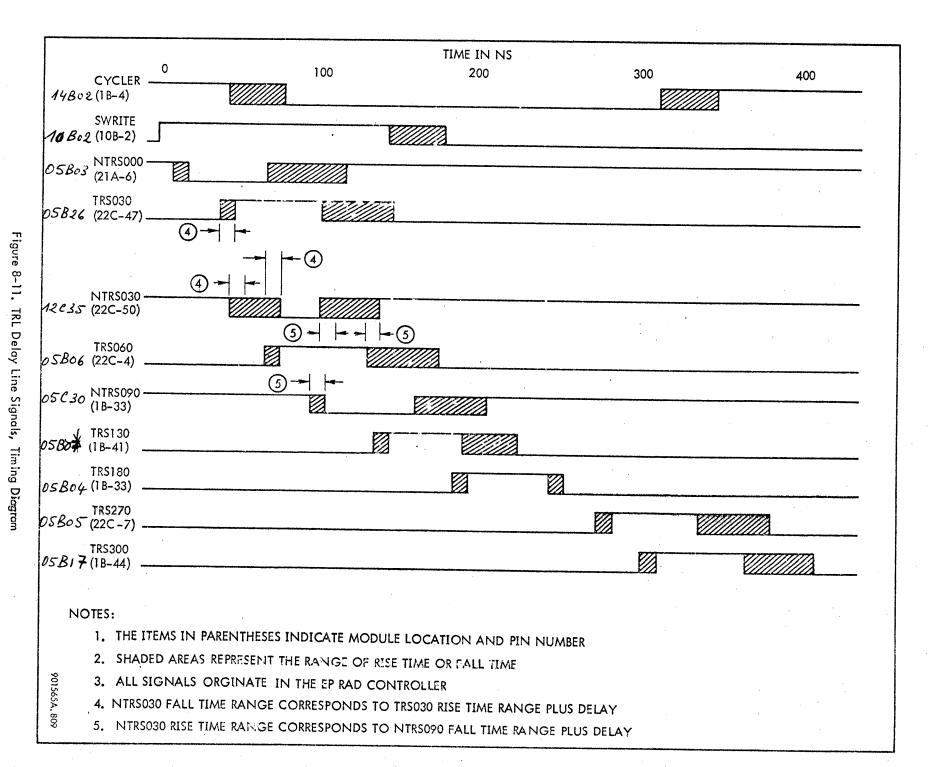

| 8-11   | TRL Delay Line Signals, Timing Diagram                   | 8-19 |

| 8-12   | Write Amplifier Output Signals, Timing Diagram           | 8-20 |

| 8-13   | Data Path Timing Signals, Timing Diagram                 | 8-21 |

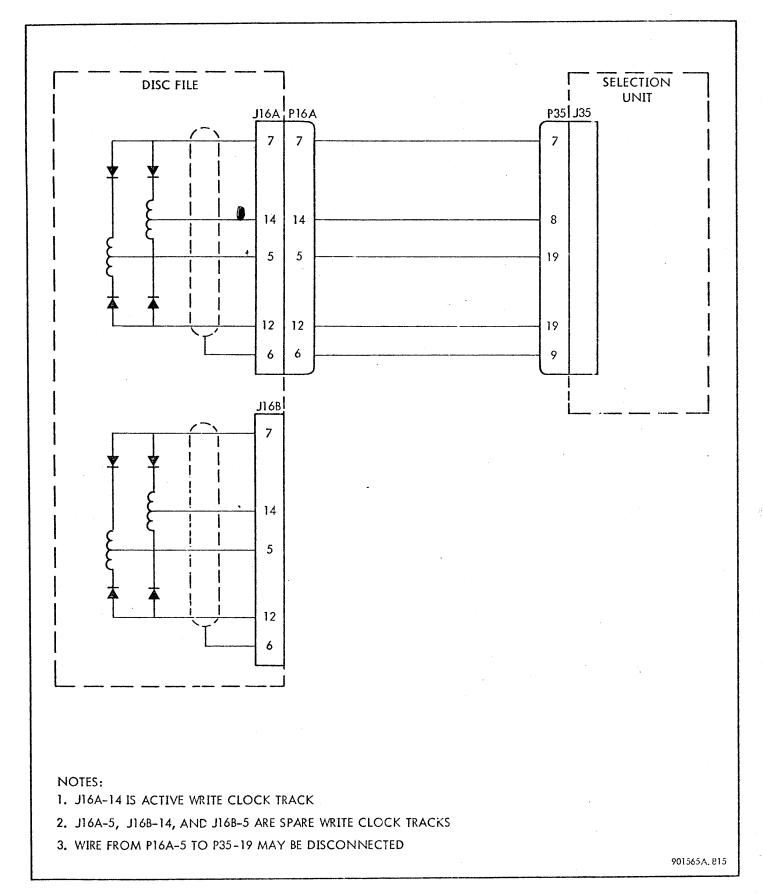

| 8-14   | Write Clock Tracks, Schematic Diagram                    | 8-29 |

| 8-15   | Head Wiring Connection Chart                             | 8-31 |

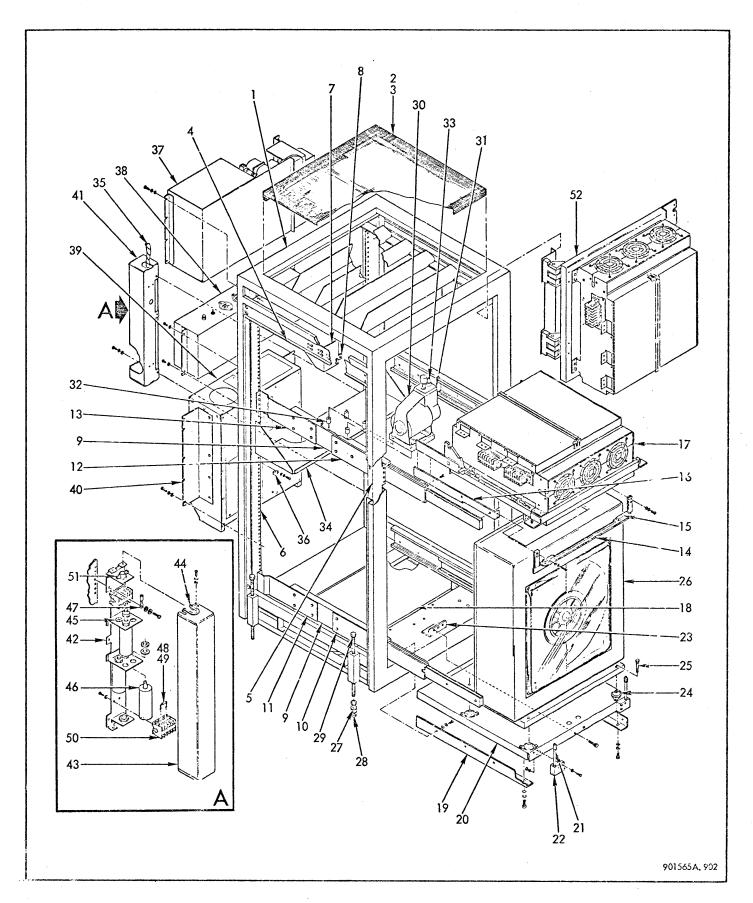

| 9-1    | Extended Performance RAD Storage Unit and RAD Controller | 9-3  |

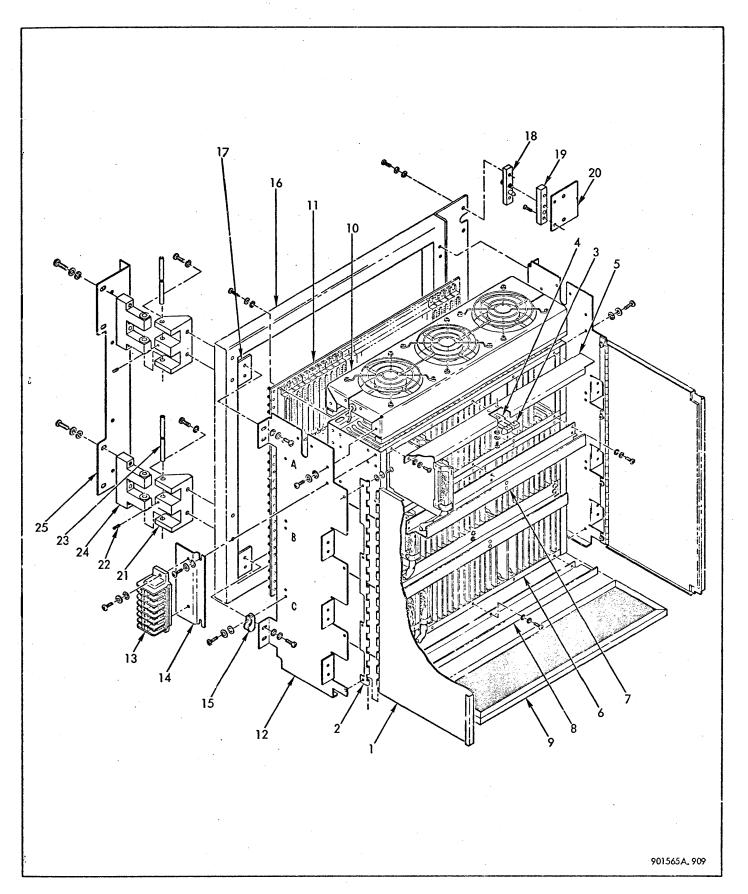

| 9-2    | RAD Storage Unit Cabinet Assembly                        | 9-5  |

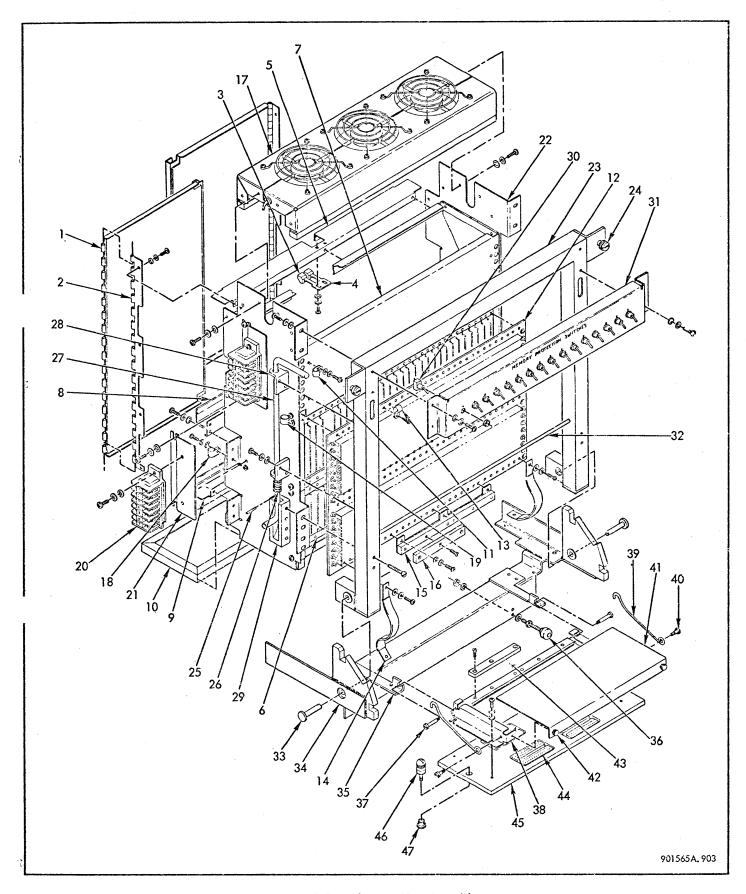

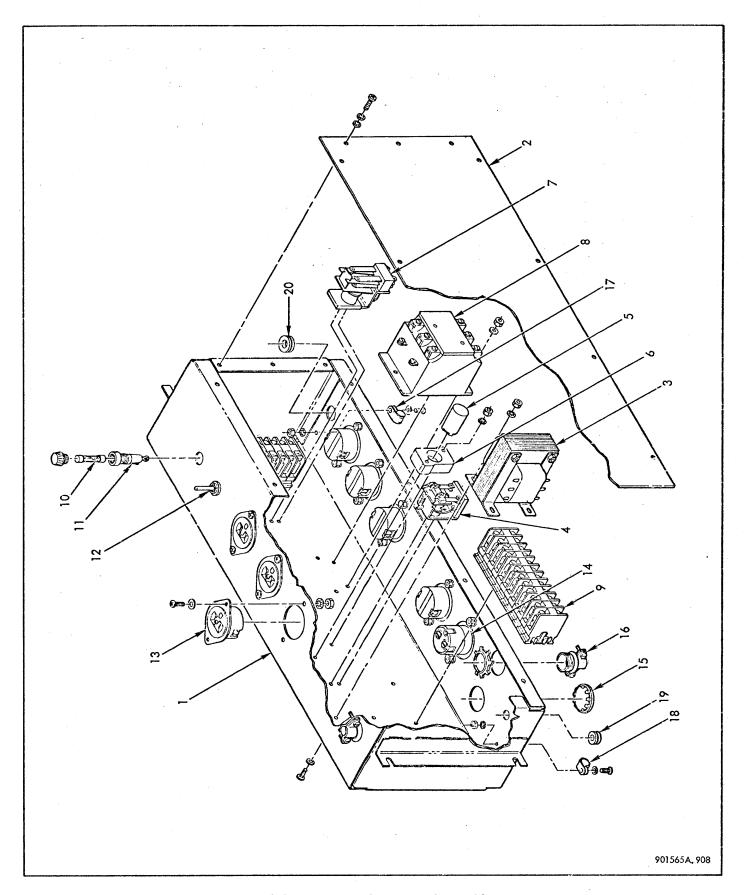

| 9-3    | Selection Unit Assembly                                  | 9-14 |

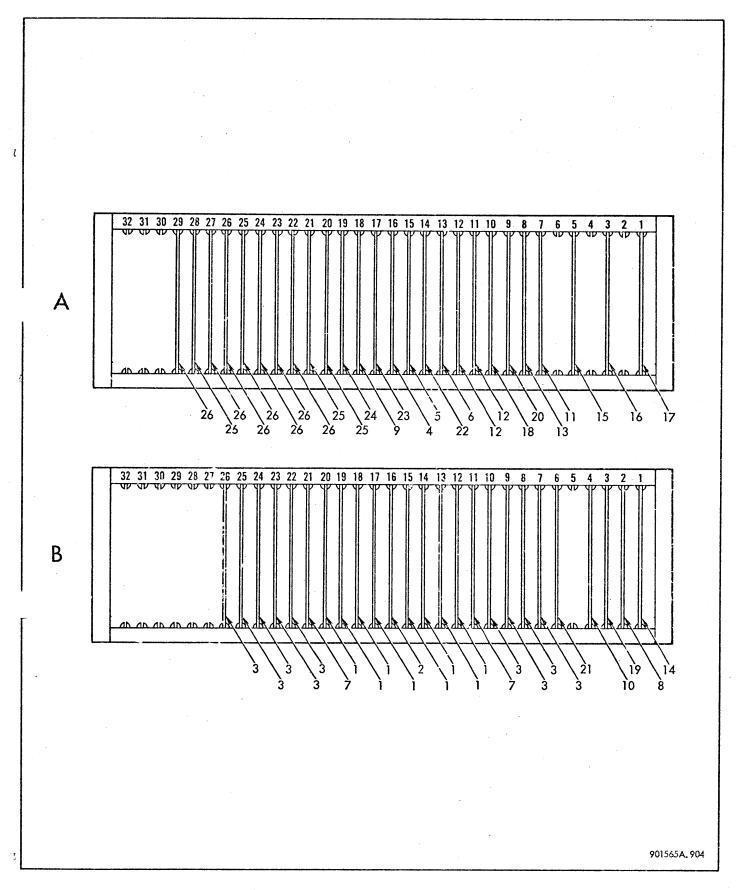

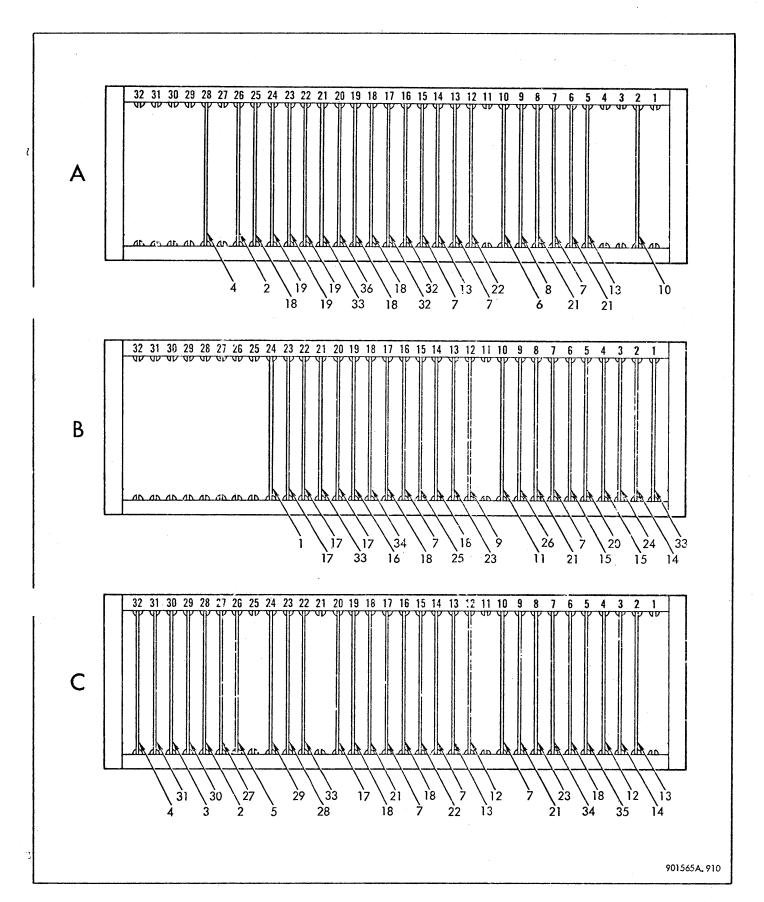

| 9-4    | Module Location (Selection Unit Assembly)                | 9-22 |

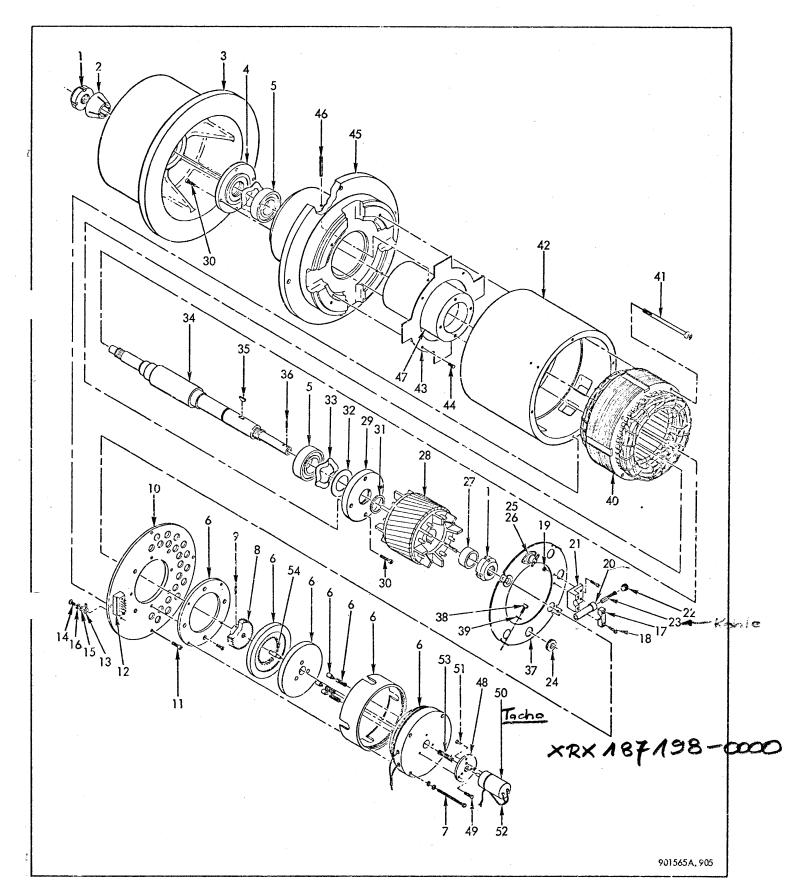

| 9-5    | Spindle and Drive Assembly                               | 9-24 |

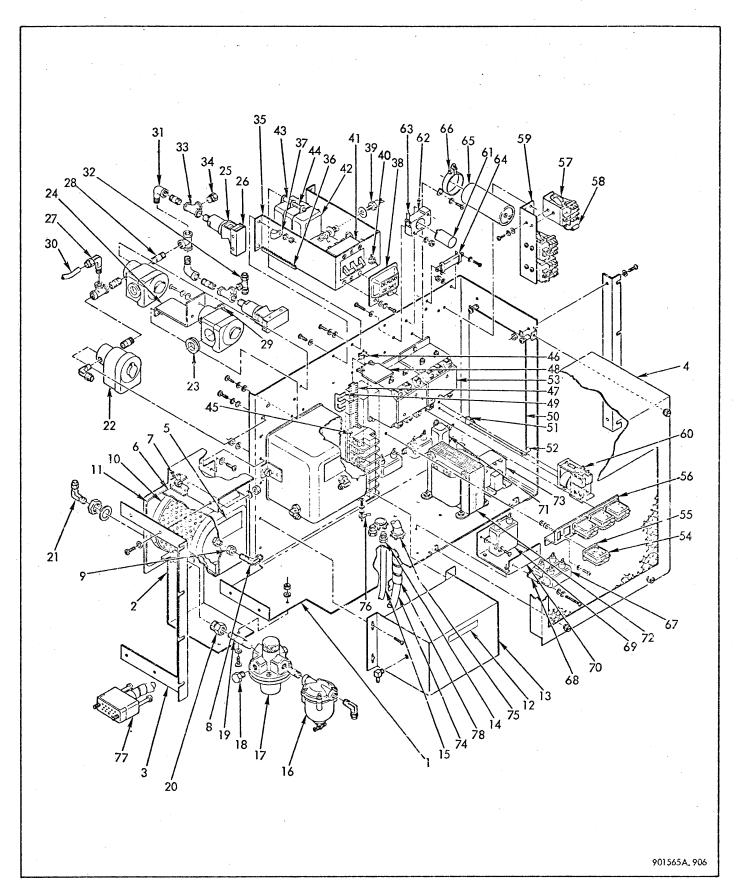

| 9-6    | Motor Control Unit Assembly                              | 9-29 |

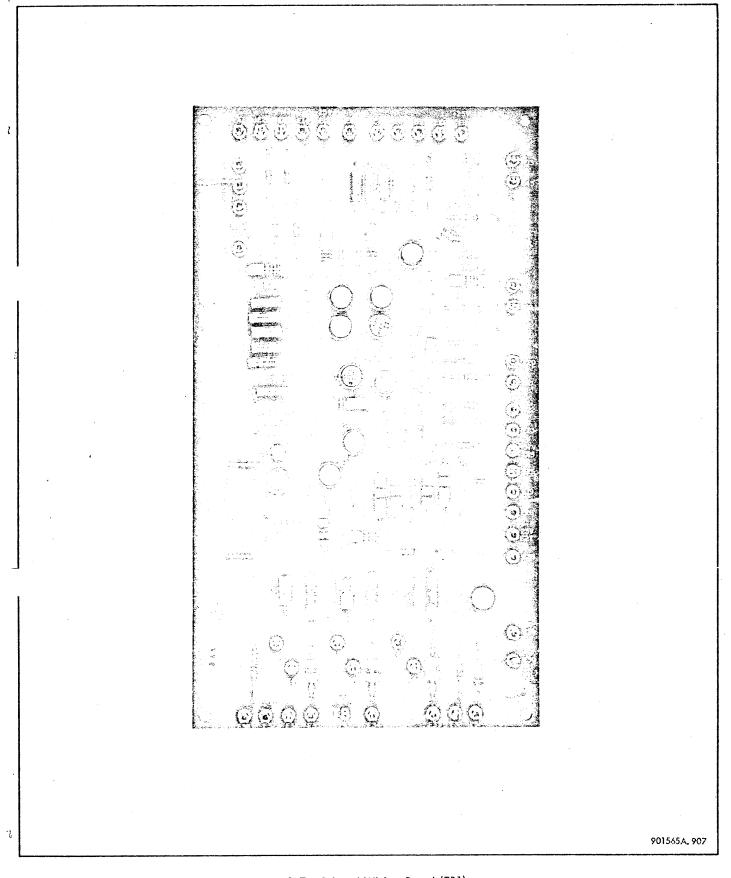

| 9-7    | Printed Wiring Board (TB1)                               | 9-40 |

| 9-8    | Power Distribution Panel Assembly                        | 9-43 |

| 9-9    | Extended Performance RAD Controller                      | 7-48 |

| 9-10   | Module Location (RAD Controller)                         | 9-54 |

|        |                                                          |      |

# LIST OF TABLES

| Table | Title                                                                  | Fage  |

|-------|------------------------------------------------------------------------|-------|

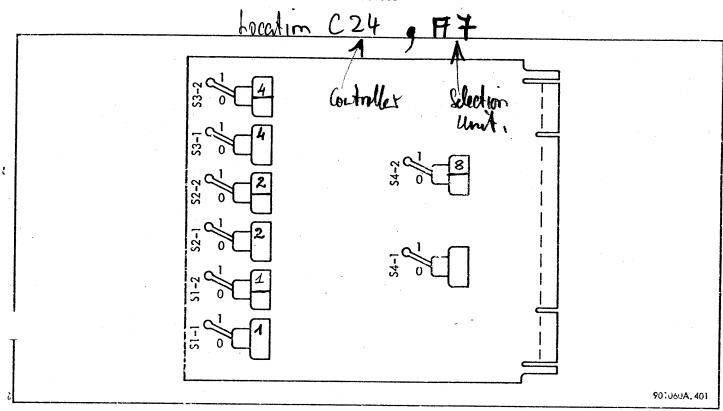

| 2-1   | EP RAD Controller Address Switch Positions (Location C24)              | 2-1   |

| 2-2   | EP RAD Storage Unit Address Switch Positions (Location A7)             | 2-1   |

| 2-3   | Portion of Machine Language Program Controlling EP RAD File            | 2-4   |

| 3-1   | Service Cycle Operations                                               | 3-6   |

| 4-1   | Information in Function Response Signals for TIO, HIO, or SIO Commands | 4-10  |

| 4-2   | Order Signals                                                          | 4-23  |

| 4-3   | Operation of the KK-Counter                                            | 4-46  |

| 4-4   | Relation Between State and Output of the L-Register                    | 4-51  |

| 4-5   | Summary of Error Flip-Flops and Signals                                | 4-76  |

| 4-6   | PET Interface Control Signals                                          | 4-84  |

| 4-7   | PET Interface Indication Signals                                       | 4-86  |

| 4-8   | AIO Command, Phase Sequence Chart                                      | 4-91  |

| 4-9   | HIO Command, Phase Sequence Chart                                      | 4-93  |

| 4-10  | SIO Command, Phase Sequence Chart                                      | 4-95  |

| 4-11  | TDV Command, Phase Sequence Chart                                      | 4-98  |

| 4-12  | TIO Command, Phase Sequence Chart                                      | 4-100 |

| 4-13  | Order Out Service Cycle, Phase Sequence Chart                          | 4-102 |

| 4-14  | Sense Order, Phase Sequence Chart                                      | 4-106 |

| 4-15  | Seek Order, Phase Sequence Chart                                       | 4-111 |

| 4-16  | Write Order or Checkwrite Order, Phase Sequence Chart                  | 4-115 |

| 4-17  | Read Order, Phase Sequence Chart                                       | 4-122 |

| 4-18  | Order In Service Cycle, Phase Sequence Chart                           | 4-129 |

### LIST OF TABLES (Cont.)

| Table        | Title                                                                      | Page         |

|--------------|----------------------------------------------------------------------------|--------------|

| 4-19         | Terminal Order Operations, Phase Sequence Chart                            | 4-133        |

| 4-20         | EP RAD Selection Unit Interface Signals                                    | 4-135        |

| 4-21         | Memory Protect Signals                                                     | 1 124        |

| 4-22         | Typical Operations of the EP RAD File                                      | 4-145        |

| 5-1          | Glossary of EP RAD File Terms                                              | 5-1          |

| 5-2          | Glossary of EP RAD Confroller Signals                                      | 5-4          |

| 5-3          | Glossary of EP KAD Selection Unit Signals                                  | 5-20         |

| 6-1          | List of Related Engineering Data                                           | 6-1          |

| 7-1          | EP RAD Storage Unit Specifications                                         | 7-1          |

| 7-2          | Connections Between EP RAD Controller and IOP                              | 7-2          |

| 7-3          | Installation Procedure Checkoff List                                       | 7-3          |

| 8-1          | Functions of PET Panel Overlay Switch Designations                         | 8-8          |

| 8-2          | lest Equipment Required for Offline Test                                   | 8-9          |

| 8 3          | Data in Bytes of Seek Order                                                | 8-10         |

|              | Locations of Y-Select Output Signals                                       | 8-16         |

| 83           | EP RAD File Program for Continuous Test (Sigma 5 or Sigma 7)               | 8-23         |

| 8-6          | Sigma 2 Machine Language Test Program for EP RAD File                      | 8-24         |

| 8-7          | Instructions Used in Sigma 2 Test Program                                  | 8-25         |

| 8-7A         | Replacement Filter Part Numbers for Motor Control Unit, Part Number 146485 | 8-28         |

| <b>8-</b> 78 | Replacement Filter Part Numbers for Motor Control Unit, Part Number 152692 | 8-28         |

| 8-8          | Summary of Logical Sparing Signals                                         | 8-30         |

| 9-1          | Extended Performance RAD Storage Unit                                      | 9-4          |

| 9-2          | RAD Storage Unit Cabinet Assembly                                          | 9-4          |

| 9-3          | Selection Unit Assembly                                                    | 9-15         |

| 9-4          | Module Locations (Selection Unit Assembly)                                 | 9. 23        |

| 9-5          | Spindle and Drive Assembly                                                 | າ. <u>25</u> |

| 9-6          | Motor Control Unit Assembly                                                | 9-30         |

| 9-7          | Printed Wiring Board TP1                                                   | 9.41         |

| 9-8          | Power Distribution Panel Assembly                                          | 9-44         |

| 9-9          | Extended Performance RAD Controller                                        | 0.49         |

| 9-10         | Module Locations (RAD Controller)                                          | 2-55         |

| 9-11         | Numerical Index                                                            | 957          |

|              |                                                                            | 7.57         |

#### LIST OF RELATED PUBLICATIONS

The following publications contain information not included in this manual but necessary for a complete understanding of the Extended Performance Rapid Access Data (EP RAD) File when used with related XDS equipment.

| Publication Title                                                                                                     | Publication No. |

|-----------------------------------------------------------------------------------------------------------------------|-----------------|

| Extended Performance RAD Storage System,<br>Models 7231/7232, Reference Manual                                        | 901557          |

| Sigma Computer Systems Interface Design<br>Manual                                                                     | 900973          |

| Power Supply Mode! PT20, Technical Manual                                                                             | 901157          |

| Sigma 5 and 7 Extended Performance Rapid<br>Access Data (RAD) File, Program No. 704978B,<br>Diagnostic Program Manual | 901540          |

| Peripheral Equipment Tester Model 7901,<br>Technical Manual                                                           | 901004          |

| Sigma 2 Computer, Technical Manual                                                                                    | 900530          |

| Sigma 2 Computer, Reference Manual                                                                                    | 900964          |

| Sigma 5 Computer, Technical Manual                                                                                    | 901172          |

| Sigma 5 Computer, Reference Manual                                                                                    | 900959          |

| Sigma 7 Computer, Technical Manual                                                                                    | 901060          |

| Sigma 7 Computer, Reference Manual                                                                                    | 900950          |

| Multiplexing Input/Output Processor, Models 8271/8471 and 8272/8472, Technical Manual                                 | 901515          |

| Selector Input/Output Processor (SIOP), Model<br>8285 and 8485, Technical Manual                                      | 901195          |

| Diagnostic Control Program for Sigma 5 and<br>Sigma 7 Computer Peripheral Devices, Ref-<br>erence Manual              | 900712          |

| Sigma 2 Systems Test Monitor, Diagnostic<br>Program Manual                                                            | 900841          |

| Sigma 5 and 7 Systems Test Monitor,<br>Diagnostic Program Manual                                                      | 901076          |

| Sigma 2 High Capacity Rapid Access Data (RAD)<br>File Test, Diagnostic Program Manual                                 | 901538          |

| Sigma 5 and 7 Relocatable Diagnostic Program Loader, Diagnostic Program Manual                                        | 900972          |

| Sigma 2 Relocatable Diagnostic Program Loader,<br>Diagnostic Program Manual                                           | 901128          |

# SECTION I

#### 1-1 SCOPE OF MANUAL

This manual provides technical information pertaining to the Extended Performance Rapid Access Data File (EP RAD file), which consists of the EP RAD Controller Model 7231 and from one to eight EP RAD Storage Units Model 7232. An EP RAD file is an item of peripheral equipment which can be used with any of the Signa series computers (Sigma 2, Sigma 5, or Sigma 7). The EP RAD file is manufactured by Xerox Data Systems, El Segundo, California.

The documents in the list of related publications should be consulted to supplement the information in this manual. A complete set of documents for this equipment consists of this manual, related publications, engineering drawings, wire lists, diagnostic programs, and other data supplied with the equipment.

#### 1-2 ORGANIZATION OF MANUAL

The information contained in this manual is organized as follows:

- a. Section I outlines the content and organization of the manual and provides a brief description of the EP RAD file and its function.

- b. Section II describes the location and function of each switch and indicator and provides simple machine language programs which illustrate the relation of the EP RAD file to the computer operation.

- c. Section III describes the operation of the EP RAD file in terms of data flow through registers in response to signals generated by the computer. No reference is made to signals or logic equations, and block diagrams and flow diagrams support the text.

- d. Section IV contains a detailed description of the operation of all circuits of the EP RAD file. The purpose of each signal, the logic equations which control the signal level, and the relations between signals are described; supporting logic diagrams, timing diagrams, and flow diagrams are included.

- e. Section V lists all signals of the EP RAD file, describes the function of each signal, and contains phase sequence charts for each EP RAD file operation.

- f. Section VI includes schematic diagrams for control panels, power distribution, terminal boards, logic diagrams,

and other engineering drawings and provides a list of engineering drawings required to supplement this manual.

- g. Section VII contains cable diagrams; module location charts; power, cooling, and space requirements; and other data required for installation, including preoperational check procedures.

- h. Section VIII provides lists of special tools and test equipment; schedules and procedures for cleaning, lubricating, and preventive maintenance testing; and procedures for performance testing, trouble analysis, and adjustment.

- Section IX contains an illustrated parts breakdown and parts list.

#### 1-3 DESCRIPTION

#### 1-4 EP RAD FILE

An EP RAD file consists of from one to eight EP RAD storage units and associated interconnecting cables. Each EP RAD storage unit consists of a cabinet that contains a disc file, an EP RAD selection unit, a power distribution punel, a moror control assembly, a Power Supply Model PT20, and interconnecting cables, wiring harnesses, and pressure lines. (See figures 1-1 and 1-2.) An EP RAD controller is collocated with one of the EP RAD storage units. (See figure 1-3.)

Each EP RAD storage unit can accommodate more than 6 million bytes of data. An EP RAD file with the maximum eight EP RAD storage units can store more than 50 million bytes of data. Data bytes may be read from, or written into, the EP RAD storage unit at an average rate of more than 350,000 bytes per second.

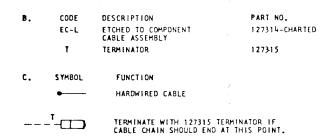

#### 1-5 EP RAD CONTROLLER

An EP RAD controller consists of three 32-module chassis and the 74 modules required for operation with an eight-bit data path. For the optional 16-bit data path, five additional modules are needed for a total of 79 modules; for the optional 32-bit data path, eight additional modules are needed for a total of 82 modules.

The EP RAD controller, which is the interface between the IOP and the EP RAD storage units, responds to command signals from the IOP. Signals returned from the EP RAD controller to the IOP indicate the status of an EP RAD storage unit and the status of the control timing of data transfers between an EP RAD storage unit and the IOP.

Figure 1-1. EP RAD Storage Unit, Front View

Figure 1-2. EP RAD Storage Unit, Rear View

Figure 1-3. EP RAD Storage Unit with EP RAD Controller, Front View

#### 1-6 EP RAD SELECTION UNIT

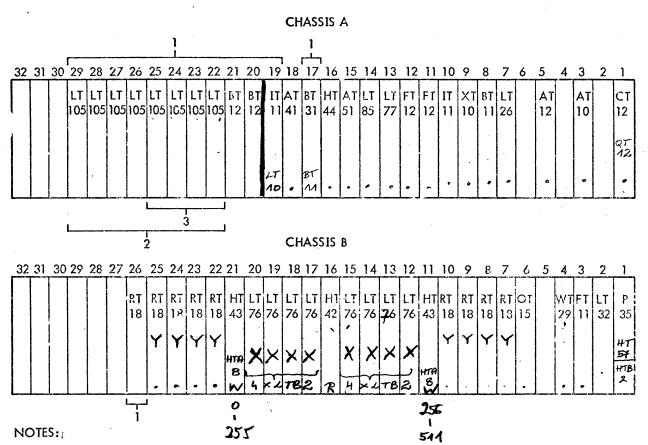

An EP RAD selection unit consists of two 32-module chassis and the 36 modules required for operation. If the logical sparing option is selected, a maximum of 13 additional modules may be used, for a total of 49 modules. The EP RAD selection unit responds to signals received from the EP RAD controller and writes data on the disc file or reads data from the disc file, as required.

#### 1-7 DISC FILE

The disc file contains four rotating magnetic surfaces for recording digital data on 512 tracks. A separate read/write head is provided for each of the 512 tracks, and 64 spare read/write heads and tracks are available. One of the magnetic surfaces has an active sector timing track and read head. (A timing track is written on each surface of the disc, so that three spare timing tracks are available.) The magnetic surfaces are sealed in a pressurized bulkhead which is maintained at a pressure higher than standard atmospheric pressure.

#### 1-8 MOTOR CONTROL ASSEMBLY

The motor control assembly controls the sequence of operations for starting and stopping the disc file motor and monitors the status of the disc file motor during operation. During

the start sequence, the motor control assembly aborts operation if the disc file does not reach 300 rpm within a preset time delay. When power is removed for shutdown or if a power failure is sensed, the motor control assembly controls both dynamic and mechanical braking.

#### 1-9 POWER DISTRIBUTION PANEL

The power distribution panel controls power from either the control console of the computer installation or the EP RAD storage unit.

#### 1-10 POWER SUPPLY MODEL PT20

Power Supply Model PT20 (also referred to in this manual as the PT20 power supply) is a standard XDS power supply and is described in detail in XDS publication No. 901157. The power input required is approximately 9A from a single-phase 117V, 60Hz source. The power supply provides outputs of +4V, +8V, -8V, +25V, -25V, and +45V, with current capability sufficient for an EP RAD selection unit and an EP RAD controller if both items are installed in the EP RAD storage unit. When an EP RAD file contains more than one EP RAD storage unit, connections from PT20 power supplies should be distributed among all phases of the three-phase source. Overvoltage and short circuit protection for the PT20 power supply is provided by modules and by a reset-table circuit breaker.

# SECTION II OPERATION AND PROGRAMMING

#### 2-1 GENERAL

The EP RAD file is controlled by programmed instructions processed by the CPU and responds to commands and orders from the IOP. Controls of the EP RAD file establish its address, indicate whether an EP RAD storage unit is online or offline, provide for write protection of selected groups of tracks, and provide for turn-on and shutdown of EP RAD file operations. Controls of the EP RAD file are described in this section. A portion of a program, in machine language, is provided to illustrate the relation between the programs and the EP RAD file operations.

#### 2-2 CONTROLS

#### 2-3 EP RAD CONTROLLER ADDRESS SWITCHES

Four switches on an LT26 Switch Comparator module (location C24, figure 7-5) establish the four-bit address of the EP RAD controller. (See table 2-1 and figure 2-1.)

Table 2-1. EP RAD Controller Address Switch Positions (Location C24)

|                 |      | [    |        | +       |

|-----------------|------|------|--------|---------|

| S4-2*           | S3-2 | S2-2 | S1-2   | Address |

| Up 1            | Down | Down | Down / | 1000    |

| Up              | Down | Down | Up     | 1001    |

| Up              | Down | Up   | Down   | 1010    |

| Up              | Down | Up   | Up     | 1011    |

| Up              | Up   | Down | Down   | 1100    |

| Up              | Up   | Down | Up     | 1101    |

| Up              | Up   | Up   | Down   | 1110    |

| Пь <sup>′</sup> | Uр   | Up   | Up     | m       |

<sup>\*</sup>Switch S4-2 position cannot be changed while the LT26 module is in place

#### 2-4 EP RAD STORAGE UNIT ADDRESS SWITCHES

Three switches on an LT26 Switch Comparator module (location A7, figure 7-4) establish a three-bit address for each EP RAD storage unit. (See table 2-2 and figure 2-1.)

#### 2-5 ONLINE/OFFLINE SWITCH

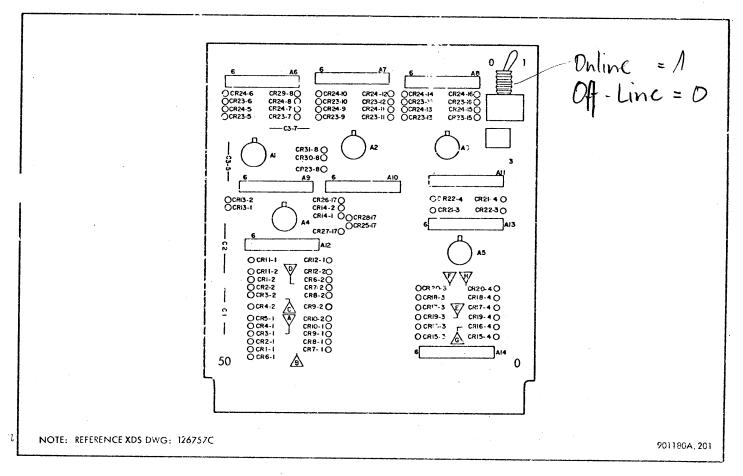

A switch on the LT25 Special Purpose module (location C23) transfers the EP RAD file from online to offline operation. When the switch is in the 0 position, the EP RAD file is offline; when the switch is in the 1 position, the EP RAD file is online. (See figure 2-2.)

#### 2-6 MEMORY PROTECTION SWITCHES

Sixteen switches on the front panel of the EP RAD selection unit (figure 1–1) may be used to prevent any CPU program from writing on selected groups of tracks on the disc file. The toggle switches are labeled MEMORY PROTECTION

Table 2-2. EP RAD Storage Unit Address Switch Positions (Location A7)

| S3 -1             | S2-1    | S1 -1  | Address* |

|-------------------|---------|--------|----------|

| Down ()           | Down () | Down 0 | 000      |

| Down              | Down    | Up     | 901      |

| <sup>1</sup> Down | Up      | Down   | 010      |

| Up                | Down    | Down   | 100      |

| Up                | Down    | Up     | 101      |

| Up                | Up      | Down   | 110      |

| Uр                | Up      | Up     | 111      |

|                   |         |        |          |

\*Up is 1; down is 0. Switch position designations cannot be read while the LT26 module is in place

Up is 1; down is 0. Switch position designations cannot be read while the LT26 module is in place

Figure 2-1. LT26 Switch Comparator Module

Figure 2-2. LT25 Special Purpose Logic Module hoodin C23

SWITCHES, and the instruction SET SWITCH IN UPPOSITION TO PROTECT INDICATED MEMORY TRACK ADDRESSES is marked on the panel. The 512 tracks are divided into 16 groups of 32 tracks each for control by MEMORY PROTECTION SWITCHES. The 32 tracks protected by each switch are indicated in decimal notation, beginning with 000 to 031 and ending with 480 to 511.

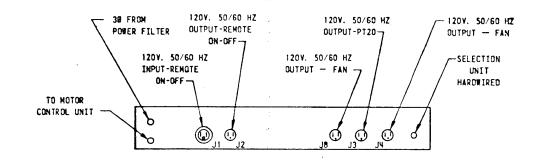

#### 2-7 POWER DISTRIBUTION PANEL

The power distribution panel contains a toggle switch labeled REMOTE-OFF-ON. No power is available for the selection unit, controller, or fans when the toggle switch is in the OFF (center) position. When the switch is in the REMOTE position, application of power is controlled from control panels of the CPU. When the switch is in the ON position, the ac power source is directly connected to the EP RAD storage unit.

#### 2-8 MOTOR CONTROL ASSEMBLY

The motor control assembly contains a circuit breaker and a toggle switch. A protective plastic cover on the circuit breaker reads EMERGENCY USE ONLY to indicate that the circuit breaker is normally ON and should not be used in routine turn-on or shutdown procedures. The POWER ON-OFF switch applies three-phase power to the motor control assembly. This power is independent of the power distribution panel.

#### 2-9 POWER SUPPLY MODEL PT20

The PT20 power supply contains a circuit breaker and a MARGIN switch. Power is applied to the PT20 power supply through the circuit breaker. The MARGIN switch, which has three positions labeled H, N, and L, is used to select a high (H), normal (N), or low (L) output voltage. Refer to XDS publication No. 901157 for additional information.

#### 2-10 OPERATING PROCEDURES

After an EP RAD file has been installed and checked as described in section VII, no special turn-on or shutdown procedures are required. The normal control positions are as follows:

- a. The EP RAD controller address switches are set to the four-bit address assigned to the controller of the EP RAD file (1000 through 1111).

- b. The EP RAD storage unit address switches are set to the three-bit address assigned to the EP RAD storage unit (000 through 111).

- c. The online/offline switch is set to 1.

- d. The MEMORY PROTECTION SWITCHES are set in the up position to protect any group of 32 tracks or are set in the down position to allow writing on tracks by CPU programs.

- e. The REMOTE-OFF-ON switch on the power distribution panel is set to REMOTE.

- f. The POWER ON-OFF switch on the motor control assembly is set to ON.

- g. The circuit breaker on the motor control chassis is ON and the protective cover is closed.

- h. The circuit breaker on the PT20 power supply is ON.

- i. The MARGIN switch on the PT20 power supply is set to  $N_{\star}$

#### 2-11 PROGRAMMING

#### 2-12 INSTRUCTIONS

Control signals and data signals exchanged between the EP RAD file and the CPU through the IOP are related to the input/output instructions. (Refer to the technical manual and reference manual associated with the computer installation for details.) After a start input/output operation (SIO), halt input/output operation (HIO), test input/output (TID), or test device (TDV) instruction is processed by the CFU, the IOP generates signals which require a response from the addressed peripheral device controller. If the EP RAD file is addressed, the IOP generates signals which contain the information required by the instruction. After an acknowledge I/O interrupt (AIO) instruction is processed by the CPU, the IOP generates signals which require a response from the highest priority peripheral device controller that has an interrupt pending. If the controller of the EP RAD file responds, the IOP returns its address and the address of the EP RAD storage unit currently stored in the unit register.

#### 2-13 SAMPLE PROGRAM

XDS publication No. 901557 describes two sample programs. One program is for use in either a Sigma 5 or a Sigma 7 computer, and one is for use in a Sigma 2 computer. A group of machine language instructions, which form a part of the Sigma 5 and 7 programming example labeled IOINTSUP, is listed in table 2-3.

#### X DS 901565

Table 2-3. Portion of Machine Language Program Controlling EP RAD File

| Instruction*           | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2280 0020              | Load immediate (LI). Causes 0000 0200 to be stored in general register 8 to permit arming I/O interrupts                                                                                                                                                                                                                                                                                                                                  |  |  |

| 6D80 1200              | Write direct (WD). This WD instruction in interrupt control mode causes arm and enable (code 010) of all group 0000 interrupts selected by a one                                                                                                                                                                                                                                                                                          |  |  |

| 220M MMMM              | Load immediate (LI). Causes a doubleword command in location M MMMM to be stored in general register 0. Value assigned to M MMMM is controlled by the program                                                                                                                                                                                                                                                                             |  |  |

| 4CAX UUUU <sup>t</sup> | Start input/output operation (SIO). Causes the operation coded by double-word command in location M MMMM (now in general register 0) to begin in EP RAD file at address UUUU. (UUUU addresses the EP RAD file controller and one of eight EP RAD storage units. The track address and the word count are contained in the doubleword.)                                                                                                    |  |  |

| 74NX SSSS <sup>†</sup> | Store conditions and floating point central (STCF). For this program, the significant part of the STCF instruction is that which causes the condition code response to the previous SIO instruction to be stored in memory location SSSS. The value of SSSS is controlled by the program. N has no significance                                                                                                                           |  |  |

| 68CX LLLL <sup>†</sup> | Branch on conditions reset (BCR). This BCR instruction forms the logical product (AND) of its R-field (1100) and the condition code saved by the previous STCF instruction. If the SIO is accepted, the logical product is zero, and the WAIT instruction in location LLLL is executed. If the SIO is not accepted, the logical product is not zero, and the next instruction in sequence is executed. LLLL is established by the program |  |  |

| 331X PPPP <sup>†</sup> | Modify and test word (MTW). If the MTW program is executed, its R-field (0001) is added to the effective word stored in the effective location of X PPPP, and the sum is stored in the effective location. Execution of this instruction causes a branch back to the main program. PPPP is established by the program                                                                                                                     |  |  |

| 2ENX RRRR <sup>†</sup> | WAIT instruction. After this instruction is executed, no other instructions are executed until an interrupt signal is received at the end of the I/O operation started by the accepted SIO instruction. The next AIO instruction in sequence is then executed. RRRR is established by the program                                                                                                                                         |  |  |

| 6EAX JJJJ              | Acknowledge I/O interrupt (AlO). Causes status bits (0 through 15) and I/O address code bits (21 through 31) from the EP RAD file to be stored in general register 10. JJJJ is established by program                                                                                                                                                                                                                                     |  |  |

<sup>\*</sup>Instructions are coded in hexadecimal notation. Symbols other than 0 through 9 and A through F are explained

<sup>&</sup>lt;sup>t</sup>X represents a three-bit index register. Additional bits are part of the data in bits 15 through 31 or are not significant

# SECTION III FUNCTIONAL OPERATION

#### 3-1 GENERAL

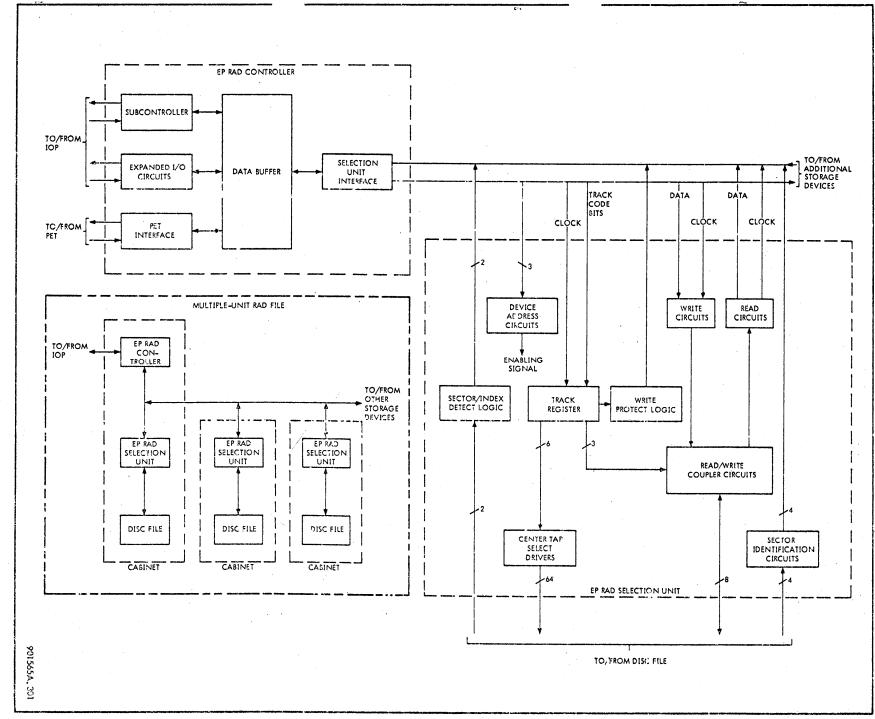

An EP RAD file consists of one EP RAD controller and from one to eight EP RAD storage units (figure 3-1). A Sigma series computer controls the EP RAD file through either a multiplexing input/output processor (MIOP) or a selector input/output processor (SIOP). The maximum capacity of each EP RAD storage unit is more than 6 million data bytes. Data bytes may be written into, or read from, the EP RAD file under program control, as described in paragraph 2-11.

Each EP RAD storage unit contains a disc file, a selection unit, a PT20 power supply, a power distribution panel, a motor control assembly, and interconnecting cables, wiring harnesses, and pressure lines. One of the EP RAD storage units contains the EP RAD controller that functions as the interface between the EP RAD file and the IOP.

The EP RAD controller and all selection units form a buffer between storage devices operating at independent clock rates. The clock rate of the computer is established by its timing circuits; the clock rate of an EP RAD storage unit is established during the writing process by the use of the Manchester encoding technique. The EP RAD storage unit may be required to read or write 12 sets of 1024 data bytes in one revolution of the disc. To meet this requirement, the EP RAD controller must accept data from one storage device at one clock rate, iemporarily store the data, and transmit the data to the other storage device at another clock rate. In addition, the EP RAD controller must make a parallel-to-serial change in format for data being transferred from the computer memory through the IOP to the EP RAD storage unit and must make a serial-to-parallel change in format for data being transferred from the EPRAD storage unit through the IOP to the computer memory.

Signals passing between the EP RAD controller and any EP RAD storage unit are exchanged through a set of transmission lines common to all EP RAD storage units. However, the EP RAD controller communicates with only one of the EP RAD storage units during any operation. The storage unit is selected by an address which is part of the command doubleword accepted by the IOP from the computer memory. Terms frequently used in this manual are defined in table 5-1.

#### 3-2 DATA ORGANIZATION

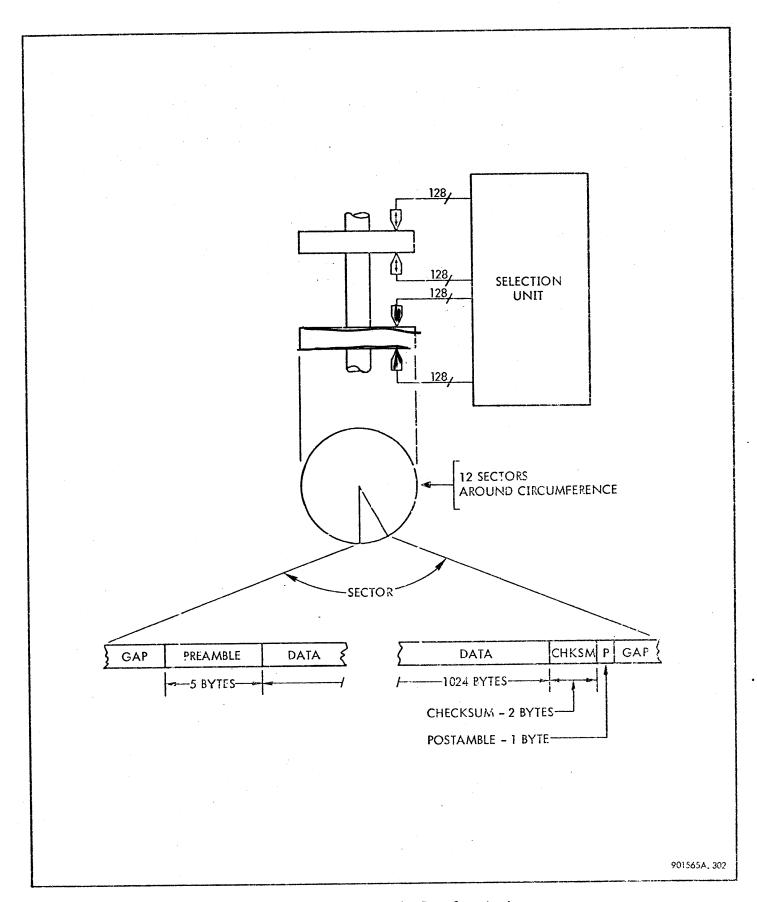

Data stored in the disc file is organized as indicated in figure 3-2. Four magnetic surfaces are used, each surface having 128 read/write heads. Data may be written by, or

read from, only one of the read/write heads at any time. The surface of the disc associated with a particular read/write head is called a track. Each track is divided into 12 equal sectors by timing signals permanently recorded on one surface of the disc. These timing signals are read by circuits of the selection unit. One of the 512 read/write heads is selected by a nine-bit track address. Each sector is identified by a four-bit sector address.

Within each sector, 1024 bytes of eight bits each are stored. The total data capacity of the disc file is obtained by multiplying 1024 bytes/sector by 12 sectors/track by 128 tracks/surface by 4 surfaces. This is a total of 6,291,456 bytes. An EP RAD file with the maximum complement of eight EP RAD storage units can store more than 50 million data bytes.

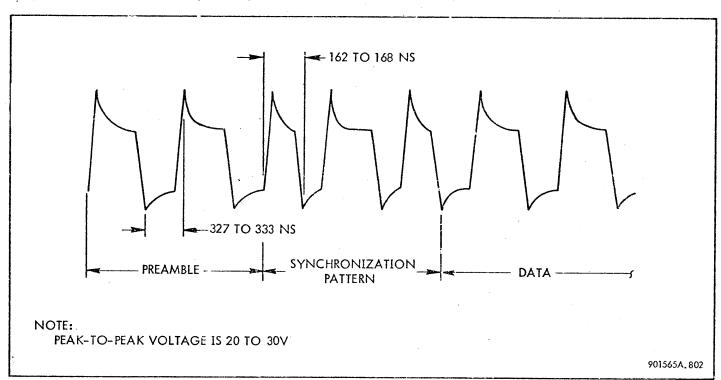

Preceding each set of 1024 data bytes is a five-byte preamble. This preamble is written by the EP RAD controller to identify the beginning of a sector of data and to synchronize controller, selection unit, and disc file operations. Following the 1024 data bytes is a two-byte checksum and a one-byte postamble. The checksum is generated by controller circuits during the write sequence, and is written after all data bytes have been stored. The postamble is a string of eight zeros which identifies the end of the sector. A gap containing no data of any kind separates the sectors. During the time that this gap is under the read/write heads, preparatory operations are performed by the controller.

#### 3-3 MECHANICAL FUNCTIONS

During operation of the EP RAD file, the read/write heads which write on (or read from) the magnetic surfaces of the disc file are held from contact with the magnetic surfaces by a thin film of air. This technique, called floating head or flying head, permits each head to be very close to a surface without contact and eliminates design problems associated with fixed heads. For example, if the position of a read/write head is fixed, the distance between the head and the moving surface varies slightly because of irregularities of surface flatness or because of a slight eccentricity of the disc axis of rotation. The variation in flux strength introduced by this variation in distance causes variation in signal levels. In addition, because the distance must be relatively large to prevent the possibility of contact, much of the strength of the magnetic field is used in the resultant air gap. However, with the flying head system of the EP RAD file, the design distance between head and surface is maintained only while the disc is spinning faster than 300 rpm. Therefore, contact between the flying heads and the disc surfaces must be relieved until the

Figure 3-1. EP RAD File, Block Diogram

Figure 3-2. EP RAD Disc File, Data Organization

300 rpm rate is attained. During a start sequence, the motor control assembly relieves the pressure holding the heads against the disc surface. During a stop sequence, the motor control assembly controls dynamic and mechanical braking of the disc. During a start sequence or a stop sequence, the motor control assembly monitors a signal which indicates the speed of the disc file motor.

# 3-4 POWER DISTRIBUTION

External three-phase ac power is applied to the power distribution panel through an rf filter assembly. The ac power passes directly from the power distribution panel to the motor control assembly. Application of ac power for the controller, selection unit, or fans may be controlled either from the operator panel of the computer or from the EP RAD storage unit. When the LOCAL/REMOTE switch on the power distribution panel is in the LOCAL position. ac power is applied directly to the PT20 power supply and he fans. When the LOCAL/REMOTE switch is in the MEMOTE position, ac power is controlled from the operator control panel of the computer. A delay circuit in the power distribution panel prevents application of ac power to more than one EP RAD storage unit at a time when ac power is first applied. This delay causes a sequential application of ac power to each EP RAD storage unit, thereby minimizing starting surges. A power fail-safe circuit senses two signals derived from the ac power source and one dc signal from the PT20 power supply. Power failure causes a controlled shutdown of the EP RAD storage unit. If the EP RAD storage unit is in communication with the IOP at the time of shutdown, a signal is sent to the IOP to indicate the unusual end.

#### 3-5 EP RAD CONTROLLER

In a computer installation, the EP RAD controller is only one of several device controllers exchanging data with the computer memory through the IOP. Two techniques are used to limit communication with the IOP to only one con-ler at any time: For some IOP commands, only one troller is addressed, and only the addressed controller can respond. For other IOP commands, a priority chain established by cable routing limits response to the highest priority controller that is awaiting that command.

The subcontroller portion of the EP RAD controller (figure 3-1) monitors signals from the ICP and determines if and how the EP RAD file responds to commands. The subcontroller responds to all control signals, either by passing the signals to other controllers associated with the computer installation or by returning signals to the IOP. The subcontroller controls exchange of data on the eight-bit data path. The expanded interface circuits provide up to 24 additional data lines when a 16-bit or a 32-bit data path is used. When the EP RAD file is operating offline, signals are received from the Peripheral Equipment Tester (PET) Model 7901 through the PET interface.

Commands from the IOP cause phase control circuits of the buffer to cycle through a definite sequence of phases.

During each phase of the sequence, the phase control circuits respond to IOP signals, selection unit signals, and internally generated signals to determine when to go from one phase to another. During this sequence of phases, data is transferred between the selection unit and the IOP through the data buffer, the selection unit interface, and the subcontroller and expanded interface circuits.

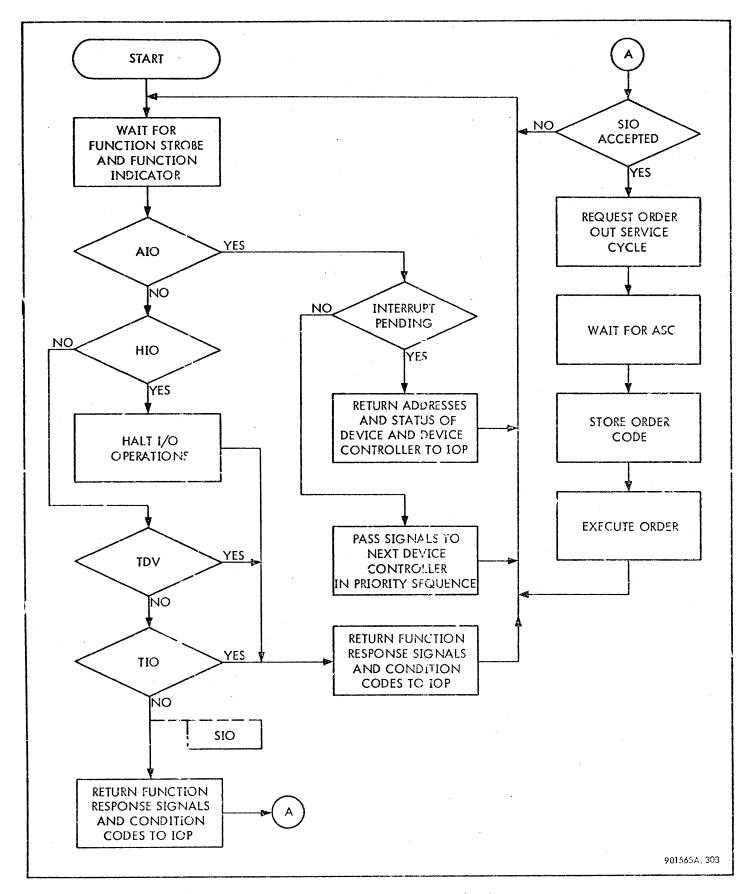

#### 3-6 IOP INTERFACE

The response of the subcontroller to IOP commands is summarized in figure 3-3. The five commands associated with CPU instructions are as follows:

| Mnemonic | <u>Function</u>                    |

|----------|------------------------------------|

| AIO      | Acknowledge input/output interrupt |

| HIO      | Halt input/output operation        |

| TDV      | Test device                        |

| TIO      | Test input/output                  |

| SIO      | Start input/output                 |

The acknowledge service call (ASC) command is generated by the IOP in response to a service call from the subcontroller.

#### 3-7 AIO Command

The AIO command, which is generated by the IOP when an interrupt is detected, is not addressed to any device or device controller. Only the highest priority device controller with an interrupt pending can respond to the AIO command. Any device controller without an interrupt pending passes the signals to the next device controller in the priority sequence. If the EP RAD controller is the highest priority device controller with an interrupt pending, it responds to the AIO command by transmitting its address and the contents of its device address register (U-register) to the IOP and by transmitting signals that indicate the cause of the interrupt. When an AIO command is accepted, the interrupt condition is cleared.

#### 3-8 HIC Command

The HIO command, which is addressed to a specific device controller, haits an input/output operation being processed by the EP RAD controller and returns function response signals and condition code signals to the IOP. These signals indicate the status of the EP RAD controller to the IOP and the CPU.

#### 3-9 TDV Command

The TDV command, which is addressed to a specific device controller, returns function response signals and condition code signals to the IOP. These signals indicate any errors

Figure 3-3. Response to IOP Commands, Flow Diagram

that occur during an input/output operation and the nature of any detected errors.

#### 3-10 TIO Command

The TIO command, which is addressed to a specific device controller, returns function response signals and condition code signals to the IOP. These signals indicate the status of the EP RAD controller to the IOP and the CPU. The TIO command performs a function similar to that of the HIO command, without causing a halt.

#### 3-11 SIO Command

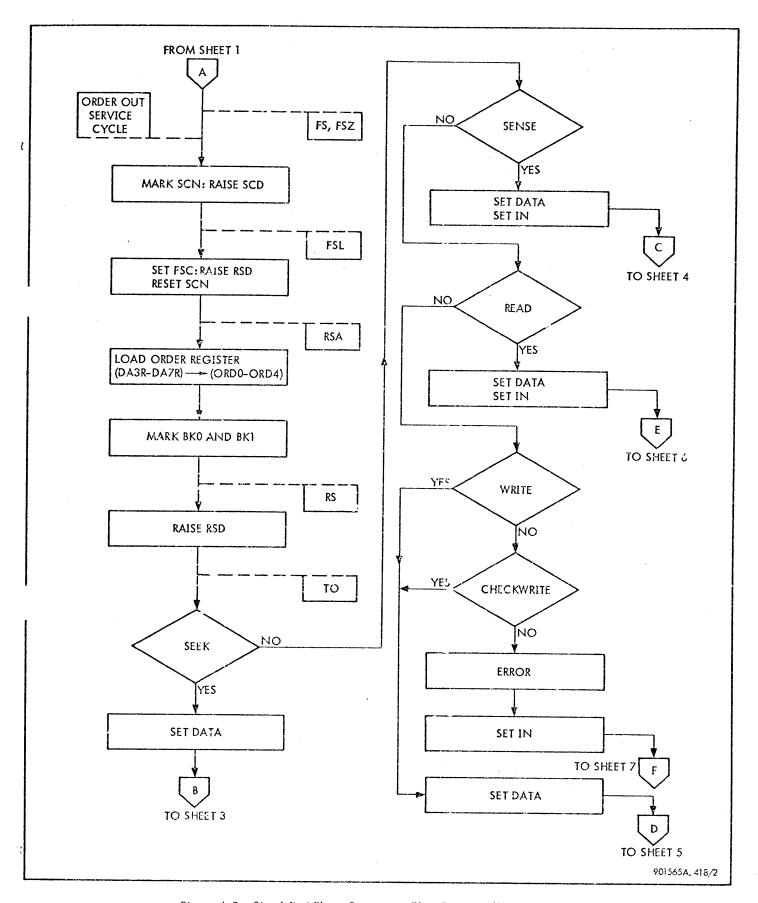

The SIO command, which is addressed to a specific device controller, returns function response signals and condition code signals to the IOP. These signals indicate the status of the EP RAD controller to the IOP and the CPU. In addition, the SIO command starts an input/output operation if the EP RAD file is ready. The first response is to request an order out service cycle from the IOP. During this service cycle, a code for one of five orders (seek, sense, read, write, or checkwrite) is stored in the order register of the EP RAD controller. A sequence of ASC commands in response to service calls from the EP RAD controller then causes the order to be executed.

#### 3-12 INTERNAL OPERATIONS

In response to an AIO, HIO, TIO, TDV, or SIO command from the IOP, the EP RAD controller gathers data available in registers and flip-flops of the controller, or from signals available at the selection unit interface, and transmits the data to the IOP as function response signals or condition code signals. If an SIO command is accepted, the I/O operation that results depends on the order received during the order out service cycle. For each order, the IOP responds to a sequence of service calls from the EP RAD controller by generating ASC commands. Each service calls identified by a two-bit code as requesting one of the four types of service cycles listed in table 3-1.

Regardless of the order received, a specific number of bytes are exchanged as the phase control circuits of the data buffer cycle through a definite sequence of phases. If a seek order is stored, subsequent data out service calls cause two bytes of data to be stored in controller registers. If a sense order is stored, subsequent data in service calls cause three bytes of data to be transmitted to the IOP. If a write order is stored, subsequent data out service calls cause data bytes in memory to be stored in the disc file. If a read order is stored, subsequent data in service calls cause data from the disc file to be stored in memory. If a checkwrite order is stored, data accepted from memory is compared with data read from the disc file. During or following execution of any of these orders, terminal order data may be received from the IOP or an order in service call may cause data to be sent to the IOP.

Table 3-1. Service Cycle Operations

| Service Cycle | Operation                                                                                                                                                                                                                                                                                                                  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Order out     | Control information is transmitted from the IOP to the controller. First service cycle of any input/output operation                                                                                                                                                                                                       |

| Order in      | Control information is transmitted from the controller to the IOP. Last service cycle of any input/output operation                                                                                                                                                                                                        |

| Data out      | Data is transmitted from the computer memory through the IOP to the disc file. Four bytes of data are transmitted during each service cycle; therefore, a rapid sequence of service cycles is required during execution of a write order or a checkwrite order. For a seek order, two data out service cycles are required |

| Data in       | Data is transmitted from the disc file through the IOP to the computer memory. Four bytes of data are transmitted during each service cycle; therefore, a rapid sequence of service cycles is required during execution of a read order. For a sense order, three data in service cycles are required                      |

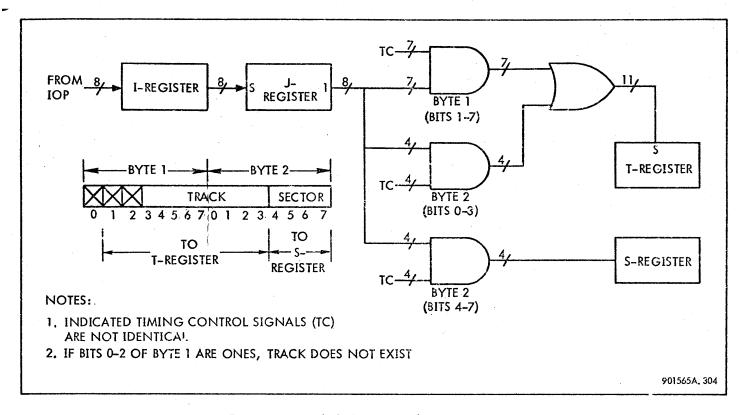

#### 3-13 Seek Order

A diagram that summarizes the transfer of data into the EP RAD controller during the execution of a seek order is presented in figure 3-4. During execution of a seek order, two Lytes of data are stored in the track address register (T-register) and the sector register (S-register). Execution of a subsequent read order, write order, or checkwrite order begins at this location in the disc file. (When no seek order is used, operations begin at the location stored in the T-register and S-register at the time that the order is received.)

A byte of data is first accepted from the IOP and is stored in the I-register. As this byte is transferred to the J-register, an additional byte is requested from the IOP. Bits 1 through 7 of the first byte are stored in the higher order flip-flops of the T-register. After the second byte is moved from the I-register to the J-register, the four higher order bits (bits 0 through 3) of the second byte are placed in the lower order flip-flops of the T-register, and the four lower order bits (bits 4 through 7) are placed in the S-register.

The byte counter of the controller identifies the bytes received and generates timing signals which control the transfer of data from the J-register. An incorrect length signal is generated by the controller if a byte count other than two is specified in the I/O doubleword associated with the seek order.

Figure 3-4. Seek Order Data Path, Block Diagram

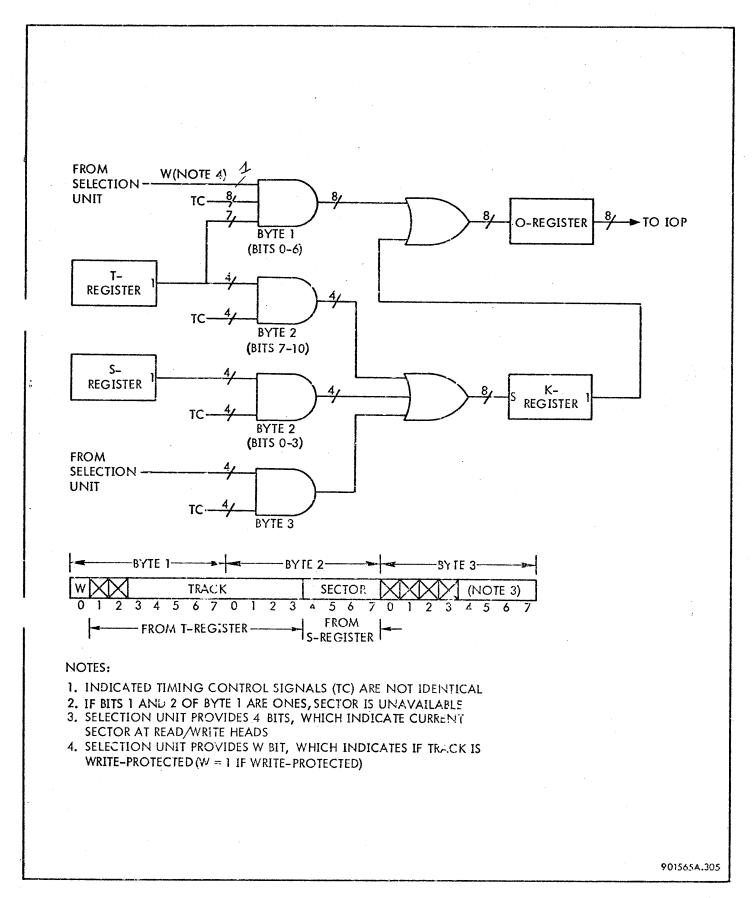

#### 3-14 Sense Order